Section 19 Serial I/O with FIFO

R01UH0134EJ0400 Rev. 4.00 Page 959 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

19.3.8 Clock Select Register (SISCR)

SISCR sets the serial clock generation conditions for the master clock. SISCR can be specified

when the TRMD1 and TRMD0 bits in SIMDR are specified as B'10.

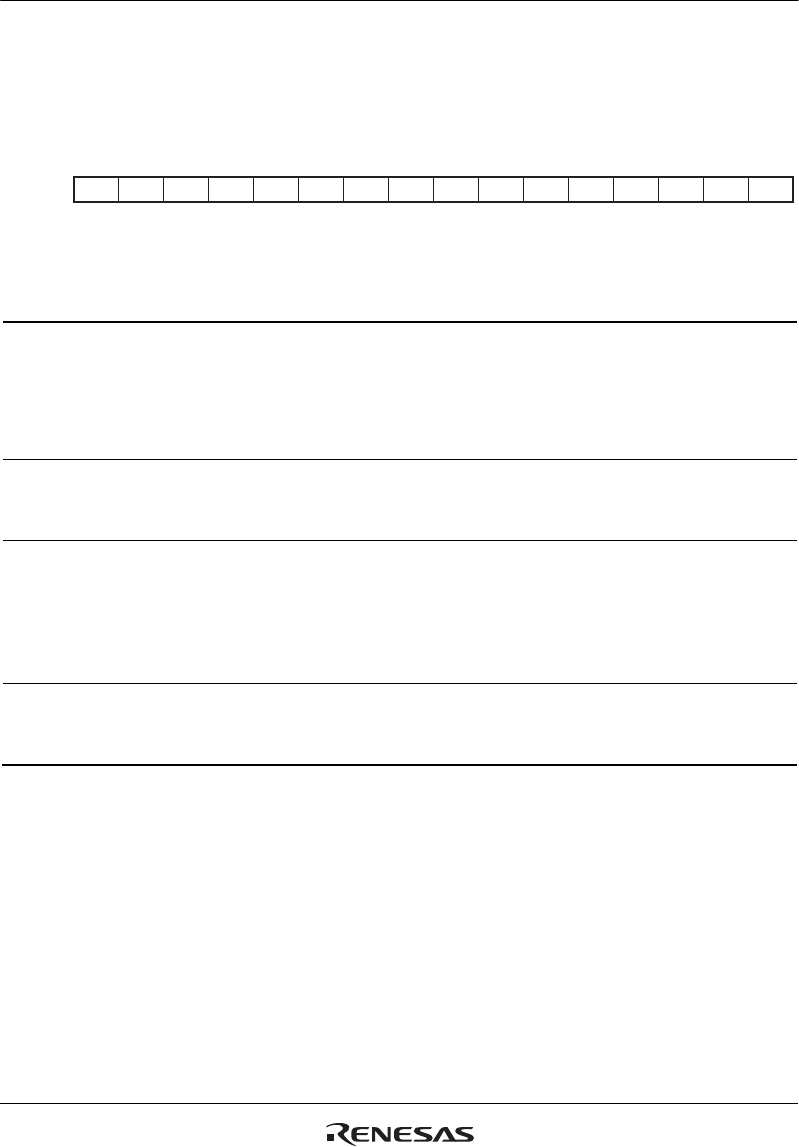

Bit:

Initial Value:

R/W:

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

0

1000000000000000

R/W R R R/W R/W R/W R/W R/W R R R R R R/W R/W R/W

MSSEL - - BRPS4 BRPS3 BRPS2 BRPS1 BRPS0 - - - - - BRDV2 BRDV1 BRDV0

Bit Bit Name

Initial

Value R/W Description

15 MSSEL 1 R/W Master Clock Source Selection

0: Uses AUDIO_X1 as the master clock

1: Uses AUDIO_CLK as the master clock

The master clock is the clock input to the baud rate

generator.

14, 13 All 0 R Reserved

These bits are always read as 0. The write value should

always be 0.

12

11

10

9

8

BRPS4

BRPS3

BRPS2

BRPS1

BRPS0

0

0

0

0

0

R/W

R/W

R/W

R/W

R/W

Prescalar Setting

Set the master clock division ratio according to the count

value of the prescalar of the baud rate generator.

The range of settings is from B'00000 (1/1) to B'11111

(1/32).

7 to 3 All 0 R Reserved

These bits are always read as 0. The write value should

always be 0.