Section 37 Electrical Characteristics

R01UH0134EJ0400 Rev. 4.00 Page 2001 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

Notes: 1. An address pin to be connected to pin A10 of SDRAM.

2. The waveform for DACKn and TENDn is when active low is specified.

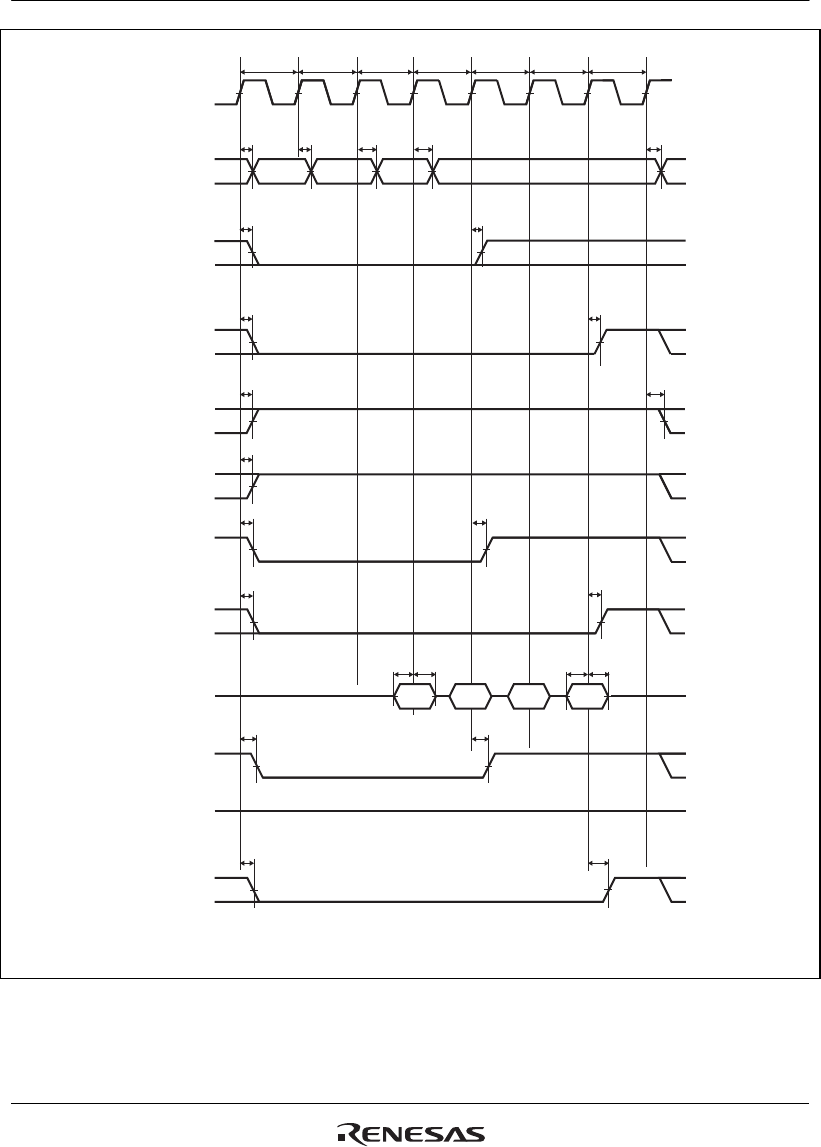

Tc2 Tc4 TdeTc1 Tc3

Td1 Td2 Td3 Td4

t

CSD1

t

AD1

t

AD1

t

AD1

t

RWD1

t

RWD1

t

CSD1

t

AD1

t

AD1

CKIO

A25 to A0

CSn

RD/WR

A12/A11

*

1

D15 to D0

t

RASD1

RAS

READ command

Column

address

t

CASD1

t

CASD1

CAS

t

BSD

t

BSD

(High)

BS

CKE

t

DQMD1

t

DQMD1

DQMxx

t

DACD

t

DACD

DACKn

TENDn*

2

t

RDH2

t

RDS2

t

RDH2

t

RDS2

t

AD1

t

AD1

Figure 37.26 Synchronous DRAM Burst Read Bus Cycle (Four Read Cycles)

(Bank Active Mode: READ Command, Same Row Address, CAS Latency 2, WTRCD = 0 Cycle)