Section 19 Serial I/O with FIFO

R01UH0134EJ0400 Rev. 4.00 Page 977 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

19.4.8 Transmit and Receive Timing

Examples of serial transmission and reception with this module are shown in figures 19.10 to

19.15.

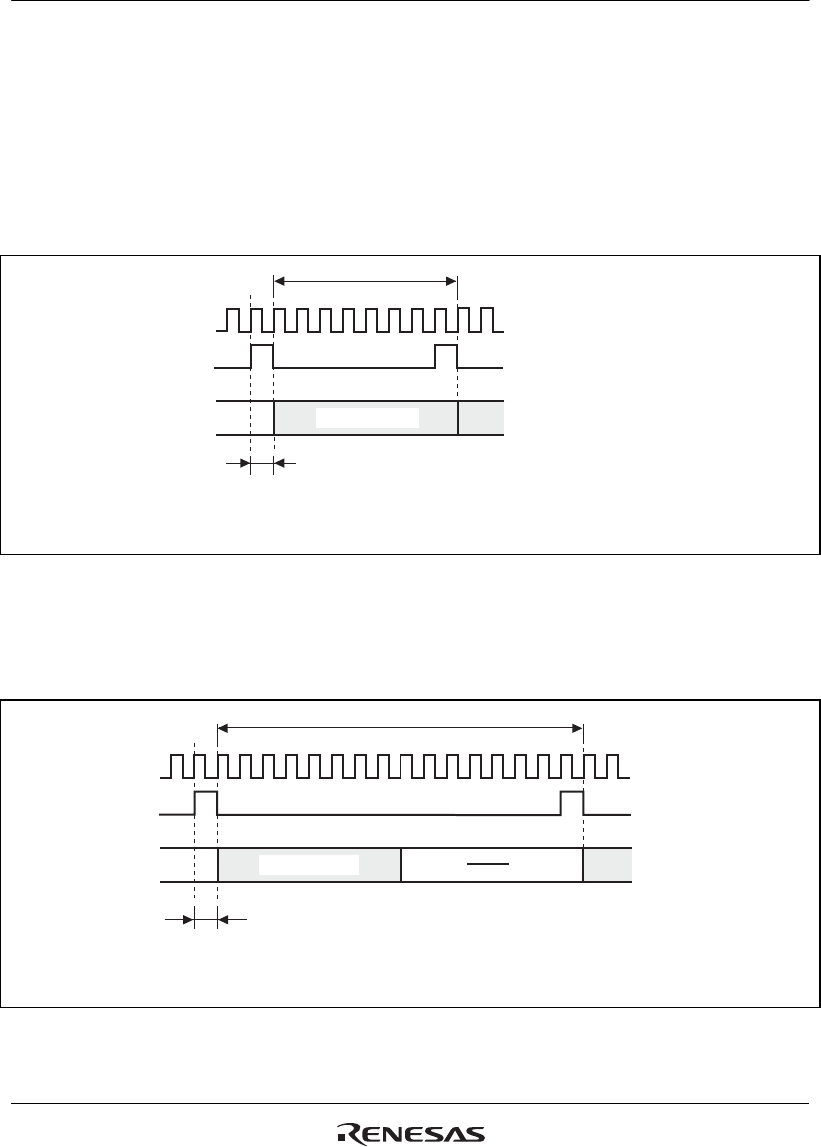

(1) 8-bit Monaural Data (1)

Falling edge sampling, slot No.0 used for transmit and receive data, an frame length = 8 bits

SIOFSCK

SIOFRxD

SIOFTxD

SIOFSYNC

L-channel data

Slot No.0

TRMD[1:0]=00 or 10,

TDLE=1,

RDLE=1,

REDG=0,

TDLA[3:0]=0000,

RDLA[3:0]=0000,

FL[3:0]=0000 (frame length: 8 bits)

TDRE=0,

RDRE=0,

TDRA[3:0]=0000,

RDRA[3:0]=0000

Specifications:

1 frame

1-bit delay

Figure 19.10 Transmit and Receive Timing (8-Bit Monaural Data (1))

(2) 8-bit Monaural Data (2)

Falling edge sampling, slot No.0 used for transmit and receive data, and frame length = 16 bits

SIOFSCK

SIOFRxD

SIOFTxD

SIOFSYNC

L-channel data

TRMD[1:0]=00 or 10,

TDLE=1,

RDLE=1,

REDG=0,

TDLA[3:0]=0000,

RDLA[3:0]=0000,

FL[3:0]=0100 (frame length: 16 bits)

TDRE=0,

RDRE=0,

TDRA[3:0]=0000,

RDRA[3:0]=0000

Slot No.0 Slot No.1

Specifications:

1 frame

1-bit delay

Figure 19.11 Transmit and Receive Timing (8-Bit Monaural Data (2))