Section 18 Serial Sound Interface

R01UH0134EJ0400 Rev. 4.00 Page 895 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

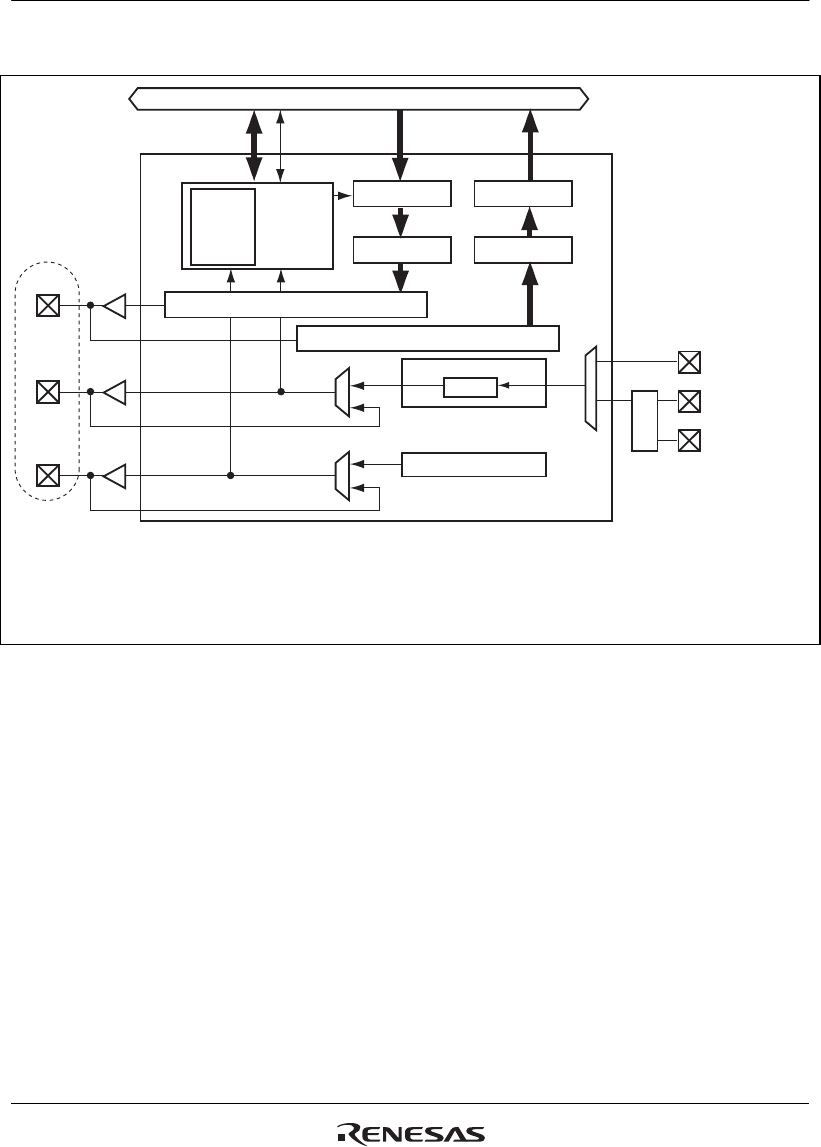

Figure 18.2 shows a block diagram of this module.

AUDIO_CLK

AUDIO_X1

AUDIO_X2

Crystal

oscillator

Peripheral bus

Serial audio bus

[Legend]

Interrupt/DMA

request

SSIDATA*

SSISCK

SSIWS

Bit counter

Control

circuit

Registers

SSICR

SSISR

SSIFCR

SSIFSR

SSICR:

SSISR:

SSITDR:

SSIRDR:

Control register

Status register

Transmit data register

Receive data register

SSITDR SSIRDR

SSIFTDR

(8-step FIFO)

SSIFRDR

(8-step FIFO)

Serial clock control

Divider

LSB

Shift register

MSB

LSB

Shift register

MSB

SSIFCR:

SSIFSR:

SSIFTDR:

SSIFRDR:

FIFO control register

FIFO status register

Transmit FIFO data register

Receive FIFO data register

Note: * In channel 0, SSIDATA can be used independently

as SSITxD for transmission and SSIRxD for reception.

Figure 18.2 Block Diagram of Serial Sound Interface