Section 25 NAND Flash Memory Controller

R01UH0134EJ0400 Rev. 4.00 Page 1297 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

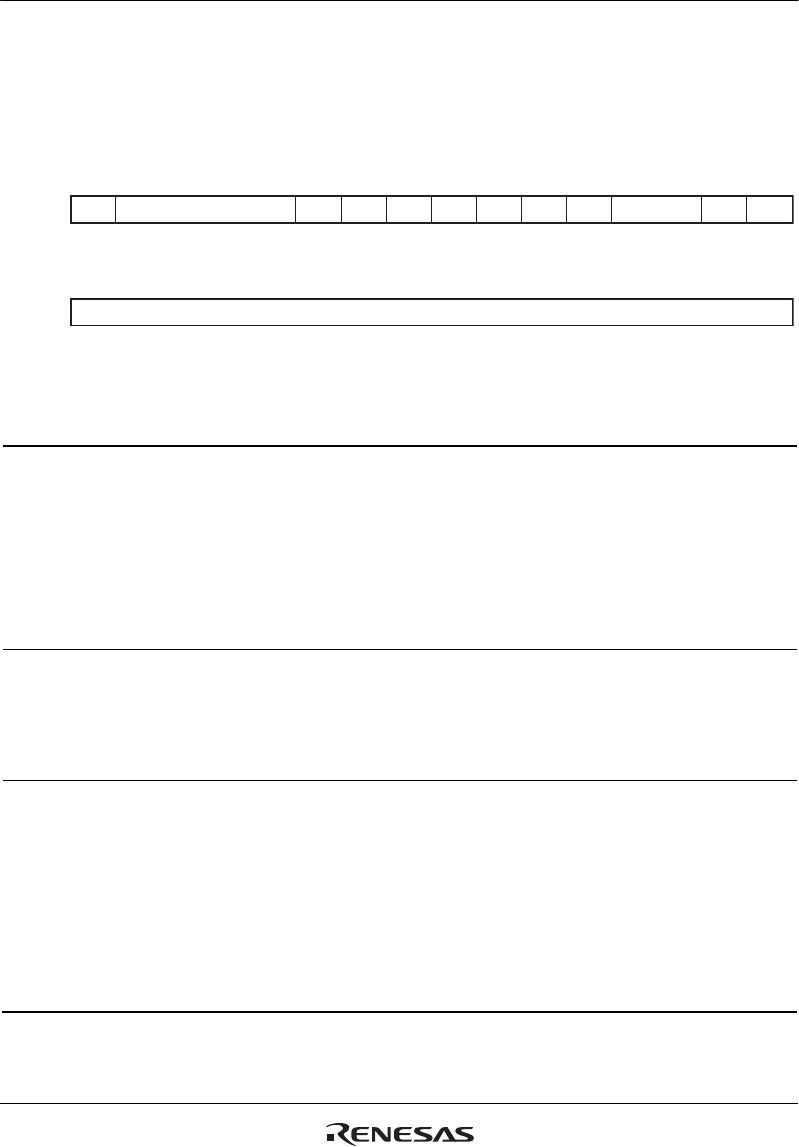

25.3.2 Command Control Register (FLCMDCR)

FLCMDCR is a 32-bit readable/writable register that issues a command in command access mode,

specifies address issue, and specifies source or destination of data transfer. In sector access mode,

FLCMDCR specifies the number of sector transfers.

Bit:

Initial value:

R/W:

Bit:

Initial value:

R/W:

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

151413121110987654321

0

0000000000000000

R/W R/W R/W R/W R/W R/W R/W R/W R R R/W R/W R/W R/W R/W R/W

0000000000000000

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

ADR

CNT2

SCTCNT[19:16]

ADR

MD

CDS

RC

DOSR - -

SEL

RW

DOA

DR

ADRCNT[1:0]

DOC

MD2

DOC

MD1

SCTCNT[15:0]

Bit Bit Name

Initial

Value

R/W Description

31 ADRCNT2 0 R Address Issue Byte Count Specification 2

Specifies the number of bytes for the address data to

be issued in address stage. This bit is used together

with ADRCNT[1:0].

0: Issue the address of byte count, specified by

ADRCNT[1:0].

1: Issue 5-byte address. ADRCNT[1:0] should be set

to 00.

30 to 27 SCTCNT

[19:16]

0000 R/W Sector Transfer Count Specification [19:16]

These bits are extended bits of the sector transfer count

specification bits (SCTCNT) 15 to 0.

SCTCNT[19:16] and SCTCNT[15:0] are used together

to operate as SCTCNT[19:0], the 20-bit counter.

26 ADRMD 0 R/W Sector Access Address Specification

This bit is invalid in command access mode. This bit is

valid only in sector access mode.

0: The value of the address register is handled as a

sector address. Use this value usually in sector

access.

1: The value of the address register is output as the

address of flash memory.

Note: Clear this bit to 0 in continuous sector access.