Section 28 Sampling Rate Converter

R01UH0134EJ0400 Rev. 4.00 Page 1639 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

28.2 Register Descriptions

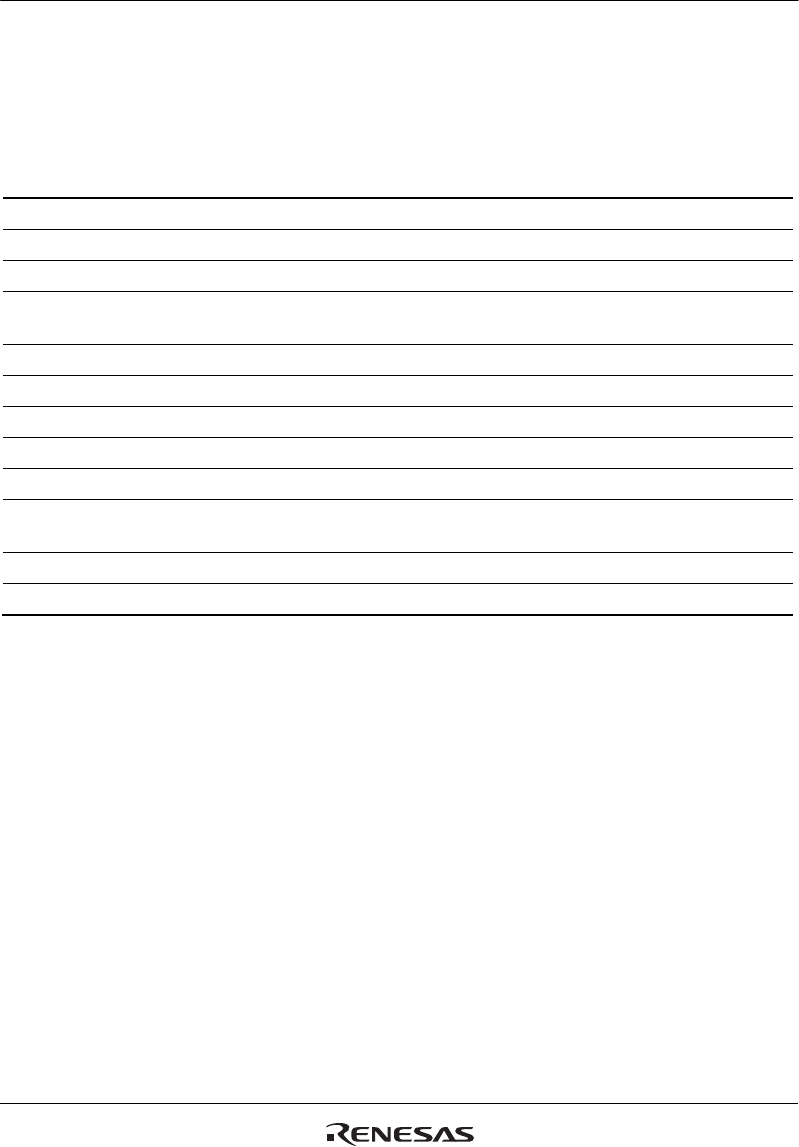

Table 28.2 shows the register configuration.

Table 28.2 Register Configuration

Register Name Abbreviation R/W Initial Value Address Access Size

Input data register_0 SRCID_0 R/W H'00000000 H'FFFF7000 16, 32

Output data register_0 SRCOD_0 R H'00000000 H'FFFF7004 16, 32

Input data control register_0 SRCIDCTRL_0 R/W H'0000 H'FFFF7008 16

Output data control

register_0

SRCODCTRL_

0

R/W H'0000 H'FFFF700A 16

Control register_0 SRCCTRL_0 R/W H'0000 H'FFFF700C 16

Status register_0 SRCSTAT_0 R/(W)* H'0002 H'FFFF700E 16

Input data register_1 SRCID_1 R/W H'00000000 H'FFFF7800 16, 32

Output data register_1 SRCOD_1 R H'00000000 H'FFFF7804 16, 32

Input data control register_1 SRCIDCTRL_1 R/W H'0000 H'FFFF7808 16

Output data control

register_1

SRCODCTRL_

1

R/W H'0000 H'FFFF780A 16

Control register_1 SRCCTRL_1 R/W H'0000 H'FFFF780C 16

Status register_1 SRCSTAT_1 R/(W)* H'0002 H'FFFF780E 16

Note: * Bits 15 to 6 and 4 are read-only. Only 0 can be written to bits 5 and 3 after having read

as 1.