Section 18 Serial Sound Interface

Page 926 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

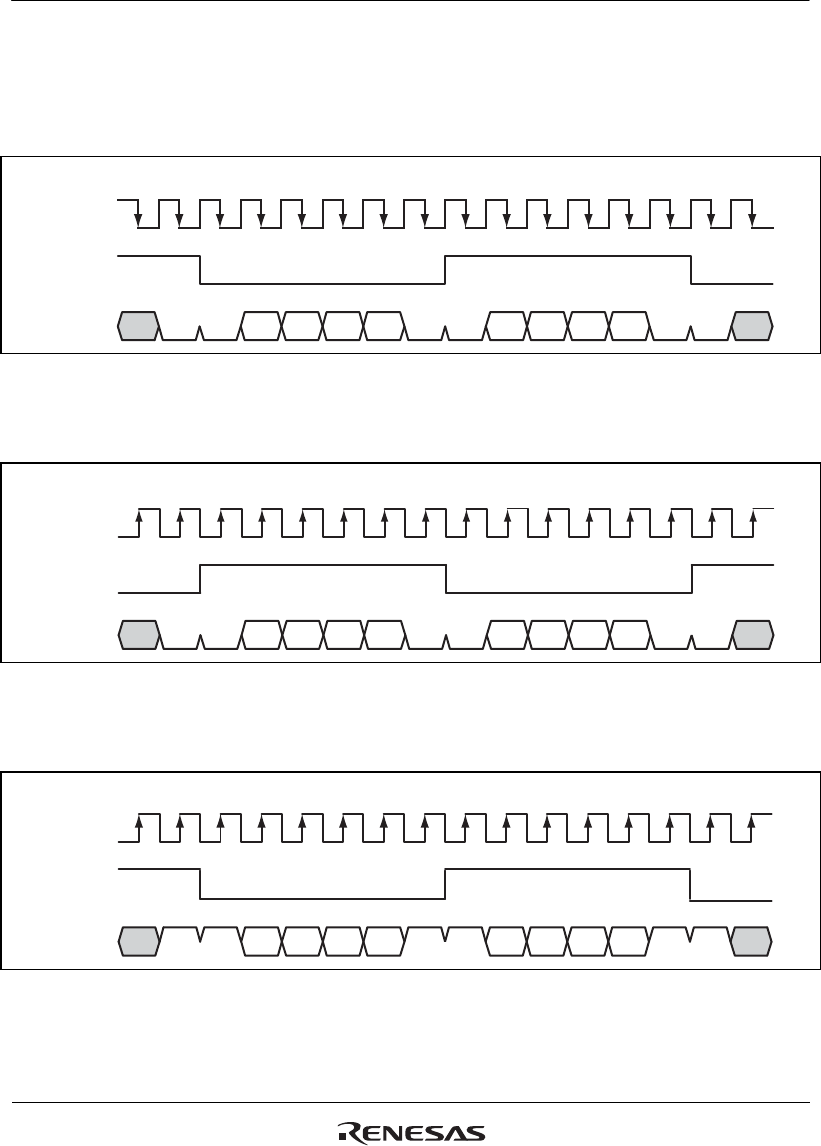

Figure 18.10 uses a system word length of 6 bits and a data word length of 4 bits. These settings

are not possible with this module but are used only for clarification of the other configuration bits.

Inverted Clock

SSISCK

SSIWS

SSIDATA

0000 00

1st Channel 2nd Channel

TD28 TD31TD31 TD30 TD29 TD28 TD31 TD30 TD29 TD28

As basic sample format configuration except SCKP = 1

Figure 18.11 Inverted Clock

Inverted Word Select

SSISCK

SSIWS

SSIDATA

0000 0

0

1st Channel

2nd Channel

TD28 TD31TD31 TD30 TD29 TD28 TD31 TD30 TD29 TD28

As basic sample format configuration except SWSP = 1

Figure 18.12 Inverted Word Select

Inverted Padding Polarity

SSISCK

SSIWS

SSIDATA

TD28 TD31

1st Channel

2nd Channel

11 11 11TD31 TD30 TD29 TD28 TD31 TD30 TD29 TD28

As basic sample format configuration except SPDP = 1

Figure 18.13 Inverted Padding Polarity