Section 37 Electrical Characteristics

Page 2040 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

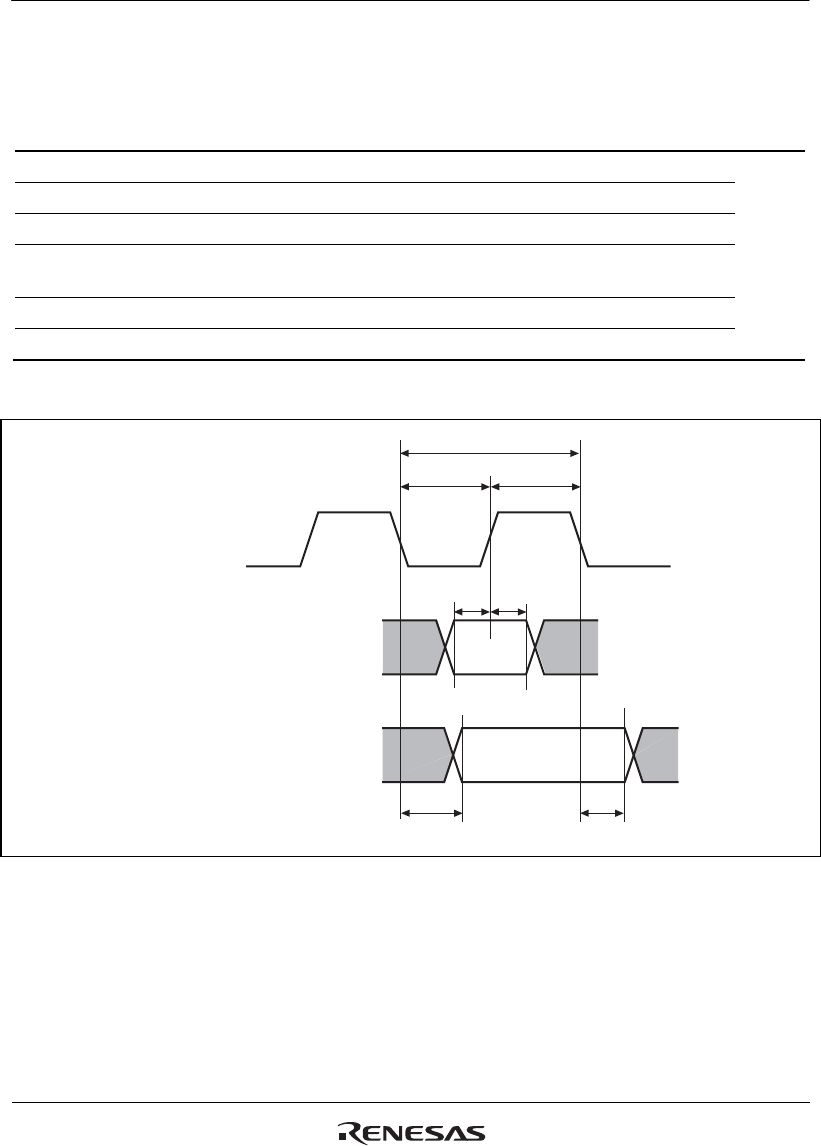

37.4.16 SD Host Interface Timing

Table 37.22 SD Host Interface Timing

Item Symbol Min. Max. Unit Figure

SD_CLK clock cycle t

SDPP 2 tpcyc ns Figure

37.75

SD_CLK clock high width tSDWH 0.4 tSDPP ns

SD_CLK clock low width tSDWL 0.4 tSDPP ns

SD_CMD, SD_D3 to SD_D0 output data delay

(data transfer mode)

tSDODLY 14 ns

SD_CMD, SD_D3 to SD_D0 input data setup tSDISU 5 ns

SD_CMD, SD_D3 to SD_D0 input data hold tSDIH 5 ns

Note: t

pcyc

indicates peripheral clock (P) cycle.

t

SDPP

t

SDWL

t

SDIH

t

SDISU

t

SDODLY

(max) t

SDODLY

(min)

t

SDWH

SD_CLK

SD_CMD, SD_D3 to SD_D0 input

SD_CMD, SD_D3 to SD_D0 output

Figure 37.75 SD Card Interface