Section 25 NAND Flash Memory Controller

R01UH0134EJ0400 Rev. 4.00 Page 1291 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

25.2 Input/Output Pins

The pin configuration of is listed in table 25.1.

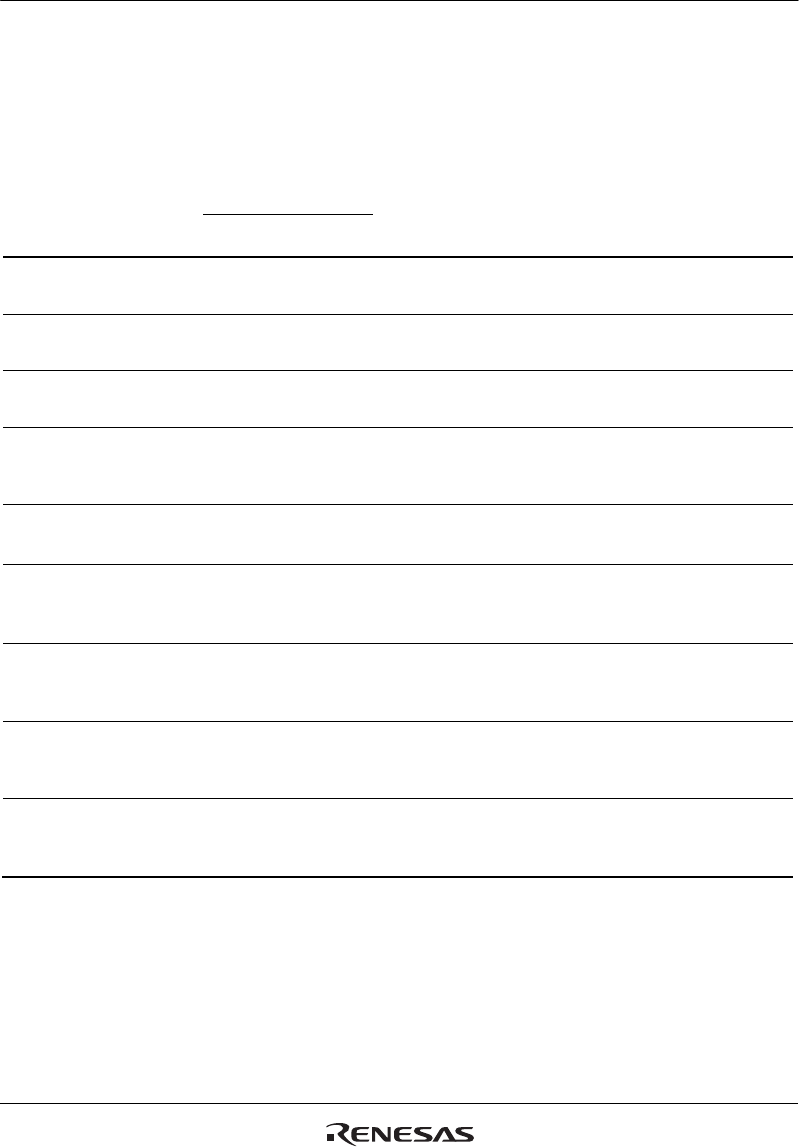

Table 25.1 Pin Configuration

Pin Name I/O

Corresponding

Flash Memory Pin

Function NAND Type

FCE

Output

CE

Flash Memory Chip Enable

Enables flash memory connected to this LSI.

NAF7 to

NAF0

I/O I/O7 to I/O0 Flash Memory Data

I/O pins for command, address, and data.

FCLE Output CLE Flash Memory Command Latch Enable

Asserted when a command is output.

FALE Output ALE Flash Memory Address Latch Enable

Asserted when an address is output and negated

when data is input or output.

FRE

Output

RE

Flash Memory Read Enable

Reads data at the falling edge of RE.

FWE

Output

WE

Flash Memory Write Enable

Flash memory latches a command, address, and

data at the rising edge of WE.

FRB Input

R/B

Flash Memory Ready/Busy

Indicates ready state at high level; indicates busy

state at low level.

*

WP

Write Protect/Reset

When this pin goes low, erroneous erasure or

programming at power on or off can be prevented.

*

SE

Spare Area Enable

Used to access spare area. This pin must be fixed

at low in sector access mode.

Note: * Not supported in this LSI.