Section 27 Video Display Controller 3

Page 1618 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

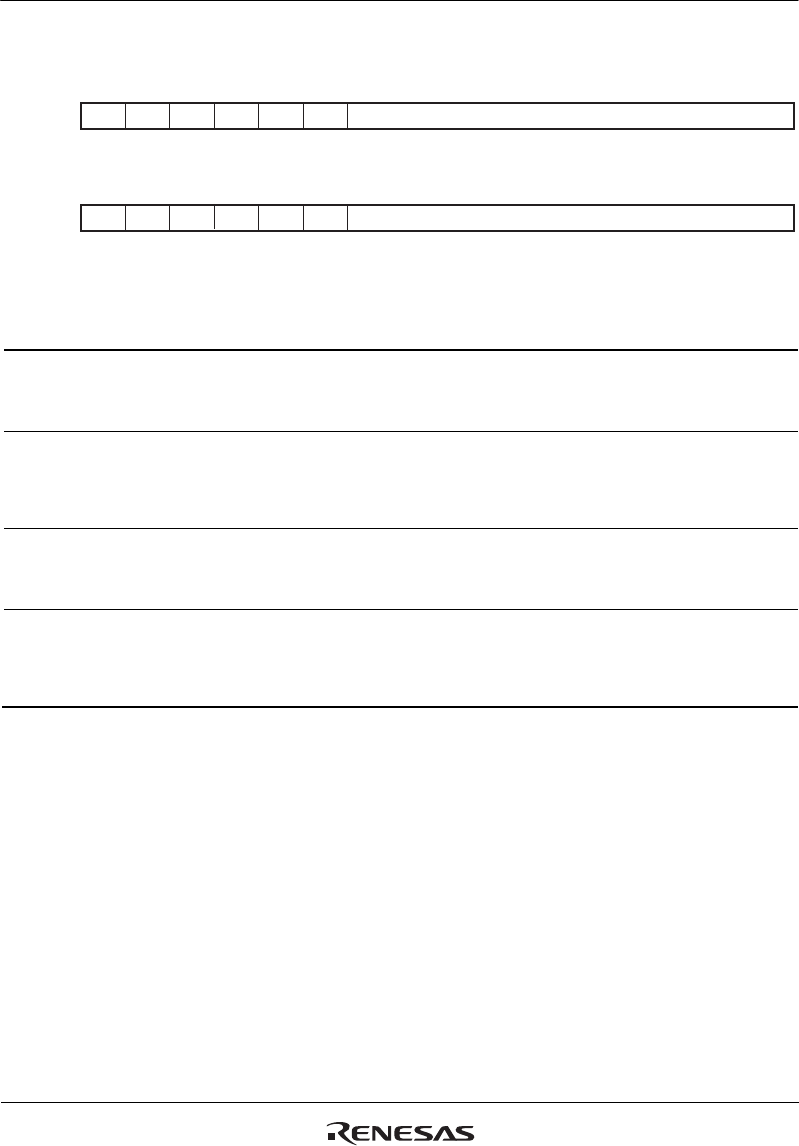

27.7.34 Vertical Sync Signal Timing Control Register (PANEL_VSYNC_TIM)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

151413121110987654321

0

0000000000000000

RRRRRRR/WR/WR/WR/WR/WR/WR/WR/WR/WR/W

0000000000000001

RRRRRRR/WR/WR/WR/WR/WR/WR/WR/WR/WR/W

------

-

VSYNC_START[9:0]

- - - - - VSYNC_END[9:0]

Bit:

Initial value:

R/W:

Bit:

Initial value:

R/W:

Bit Bit Name

Initial

Value R/W Description

31 to 26 All 0 R Reserved

These bits are always read as 0. The write value

should always be 0.

25 to 16 VSYNC_START

[9:0]

H'000 R/W These bits specify in number of lines the interval

between the reference vertical sync signal and the

point where the vertical sync signal (VSYNC) for

panel is set to 1.

15 to 10 All 0 R Reserved

These bits are always read as 0. The write value

should always be 0.

9 to 0 VSYNC_END

[9:0]

H'001 R/W These bits specify in number of lines the interval

between the reference vertical sync signal and the

point where the vertical sync signal (VSYNC) for

panel is cleared to 0.

Note: Be sure to satisfy VSYNC_START VSYNC_END; otherwise, correct operation is not

guaranteed.