Section 22 Renesas SPDIF Interface

Page 1188 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

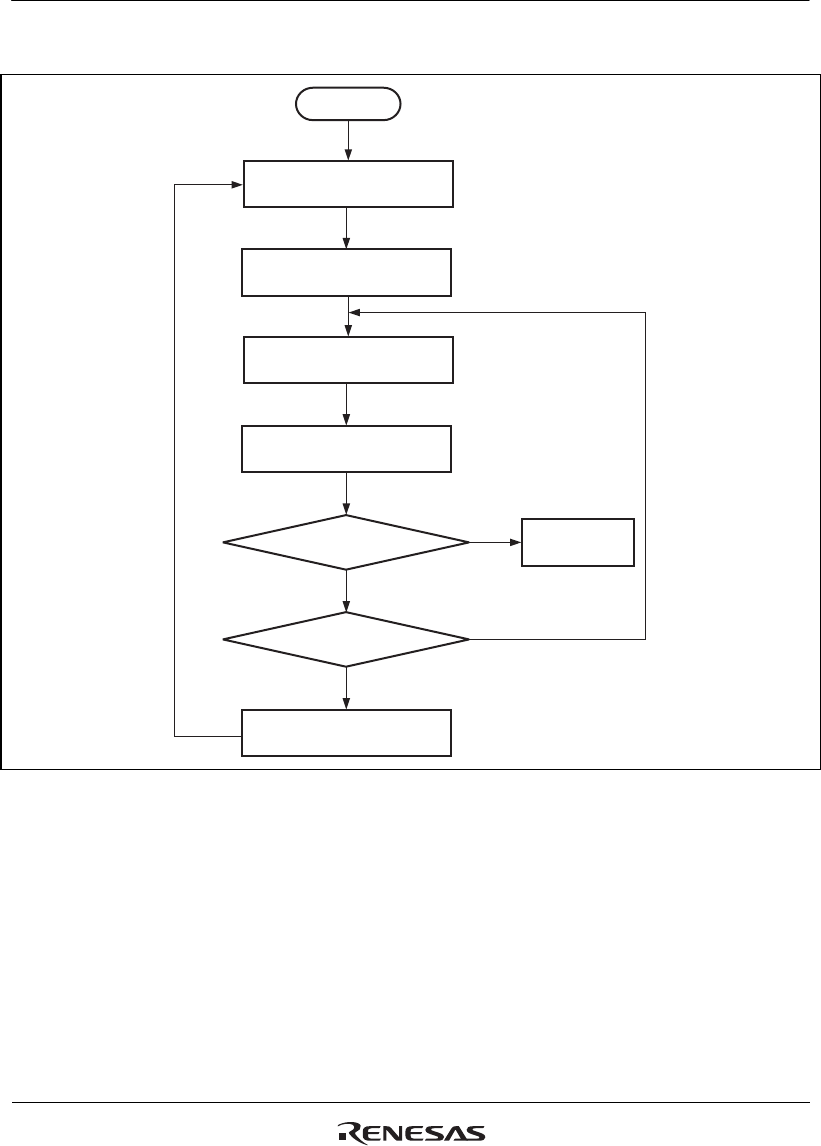

Figure 22.8 illustrates the receiver data transfer using interrupts.

Start

Idle

Wait for interrupt

Error detected?

No

Yes

No

Set control bit enabled

(RCBI)

Load left or right audio

channel data

Enter idle state?

Yes

Error handling

Set control bit disabled

(RCBI)

Figure 22.8 Receiver Data Transfer Flow Diagram - Interrupt Driven

Interrupts to indicate that the channel status information register is full occur after frame 30 has

been received and only if the information has changed. When the first four bytes have been stored

an interrupt occurs.