Section 35 Motor Control PWM Timer

R01UH0134EJ0400 Rev. 4.00 Page 1843 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

(4) Next Frame

When a compare match occurs between PWCNT_n and PWCYR_n, data is transferred from the

buffer register to the duty register. PWCNT_n is reset and starts counting up from H'000. The

CMF bit in PWCR_n is set, and if the IE bit in PWCR_n has been set, an interrupt can be

requested or the direct memory access controller can be activated.

(5) Stopping

When the CST bit in PWCR_n is cleared to 0, PWCNT_n is reset and stops. All PWM outputs go

low (or high if the corresponding bit in PWPR_n is set to 1).

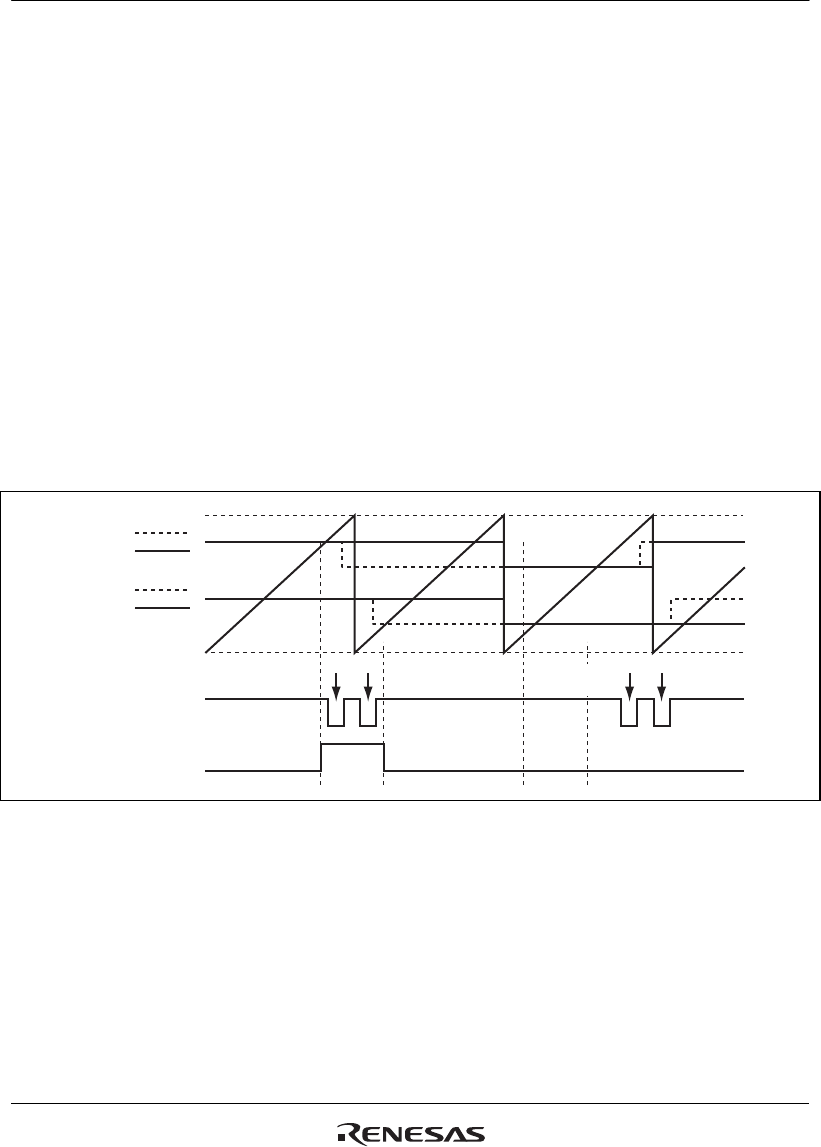

35.5.2 Buffer Transfer Control

Setting a corresponding bit in the PWM buffer transfer control register disables a buffer transfer

on compare match. This prevents the output from changing when compare match occurs while the

buffer register is being changed. A buffer transfer on compare match is resumed after cleaning the

bit.

PWBFR_1A

PWCYR

PWCNT

Write

PWDTR_1A

PWMBTCR

Buffer updated

(PWBFR_1A)

Buffer updated

(PWBFR_1C)

Buffer updated

(PWBFR_1A)

Buffer updated

(PWBFR_1C)

Disabled Enabled

Disabled: 1

Enabled: 0

PWBFR_1C

PWDTR_1C

Figure 35.8 Disabling Buffer Transfer