Section 37 Electrical Characteristics

R01UH0134EJ0400 Rev. 4.00 Page 2019 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

37.4.8 Renesas Serial Peripheral Interface Timing

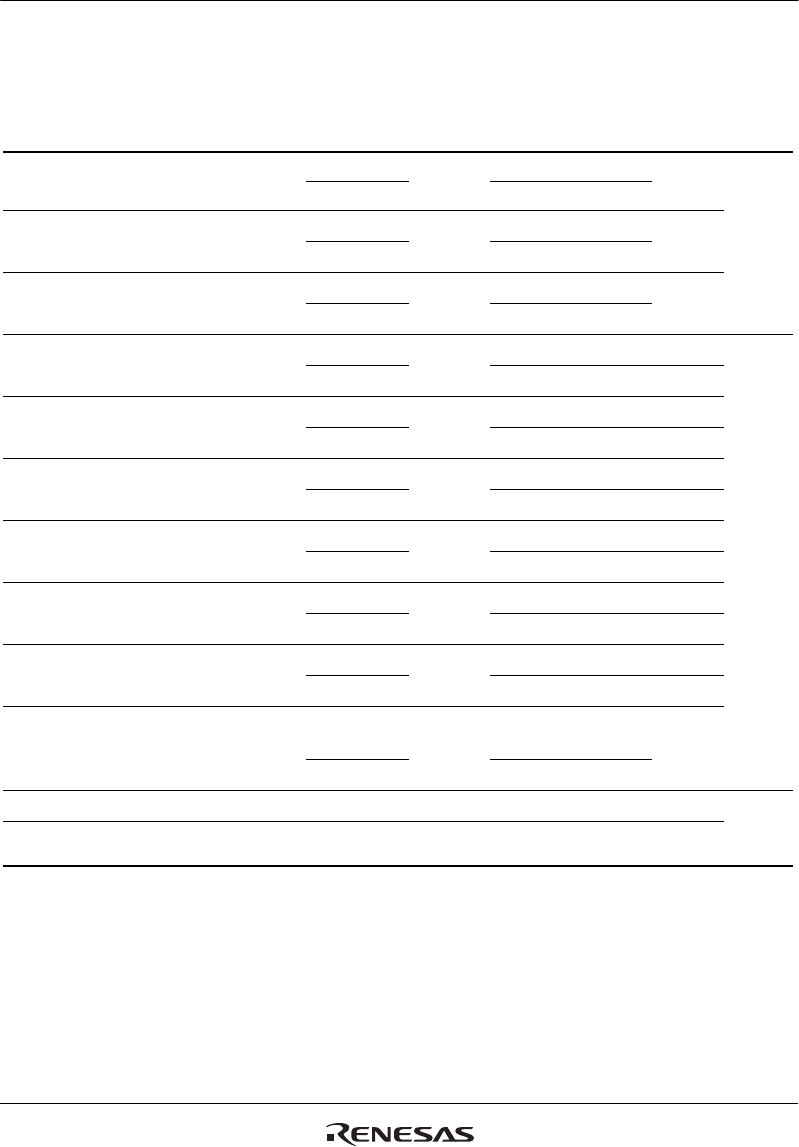

Table 37.12 Renesas Serial Peripheral Interface Timing

Item Symbol Min. Max. Unit Figure

RSPCK clock cycle Master tSPcyc 2 4096 tcyc

Figure

37.47

Slave 8 4096

RSPCK clock high pulse width Master tSPCKWH 0.4

tSPcyc

Slave 0.4

RSPCK clock low pulse width Master tSPCKWL 0.4

tSPcyc

Slave 0.4

Data input setup time Master tSU 15 ns Figures

37.48

to

37.51

Slave 0 tcyc

Data input hold time Master tH 0 ns

Slave 4 tcyc

SSL setup time Master tLEAD 1 8 tSPcyc

Slave 4 tcyc

SSL hold time Master tLAG 1 8 tSPcyc

Slave 4 tcyc

Data output delay time Master tOD 21 ns

Slave 4 tcyc

Data output hold time Master tOH 5 ns

Slave 3 tcyc

Continuous transmission delay time Master tTD 1 tSPcyc

2 tcyc

8 tSPcyc

2 tcyc

ns

Slave 4 tcyc

Slave access time tSA 4 tcyc Figures

37.50,

37.51

Slave out release time tREL 3 tcyc