Section 9 Bus State Controller

R01UH0134EJ0400 Rev. 4.00 Page 247 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

Bit Bit Name

Initial

Value R/W Description

8 to 0 All 0 R Reserved

These bits are always read as 0. The write value

should always be 0.

9.4.3 CSn Space Wait Control Register (CSnWCR) (n = 0 to 6)

CSnWCR specifies various wait cycles for memory access. The bit configuration of this register

varies as shown below according to the memory type (TYPE2 to TYPE0) specified by the CSn

space bus control register (CSnBCR). Specify CSnWCR before accessing the target area. Specify

CSnBCR first, then specify CSnWCR.

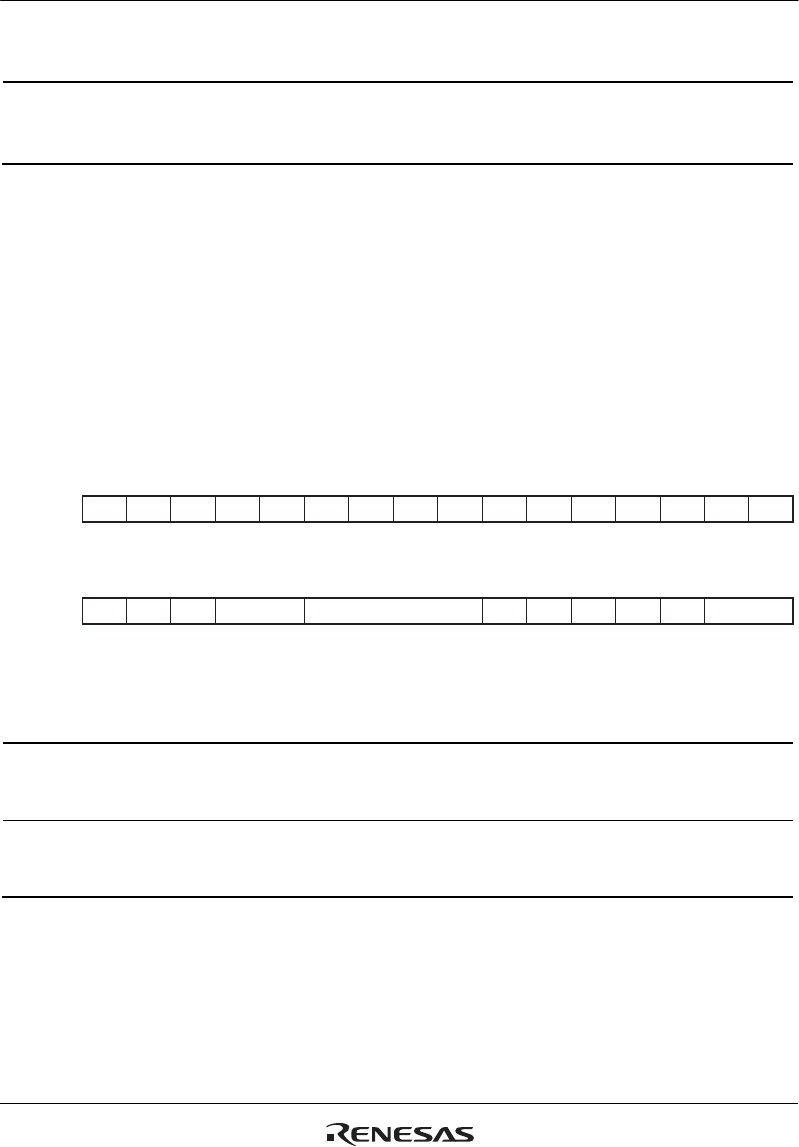

(1) Normal Space, SRAM with Byte Selection, and MPX-I/O

CS0WCR

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

0

0000000000000000

R R R R R R R R R R R/W R/W R R R/W R/W

0000010100000000

R R R R/W R/W R/W R/W R/W R/W R/W R R R R R/W R/W

Bit:

Initial value:

R/W:

Bit:

Initial value:

R/W:

-----------* BAS - - -* -*

- - - SW[1:0] WR[3:0] WM - - - - HW[1:0]

Bit Bit Name

Initial

Value R/W Description

31 to 22 All 0 R

Reserved

These bits are always read as 0. The write value

should always be 0.

21 * 0 R/W

Reserved

Set this bit to 0 when the interfaces for normal space

or for SRAM with byte selection are used.