Page 2094 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

Item Page Revision (See Manual for Details)

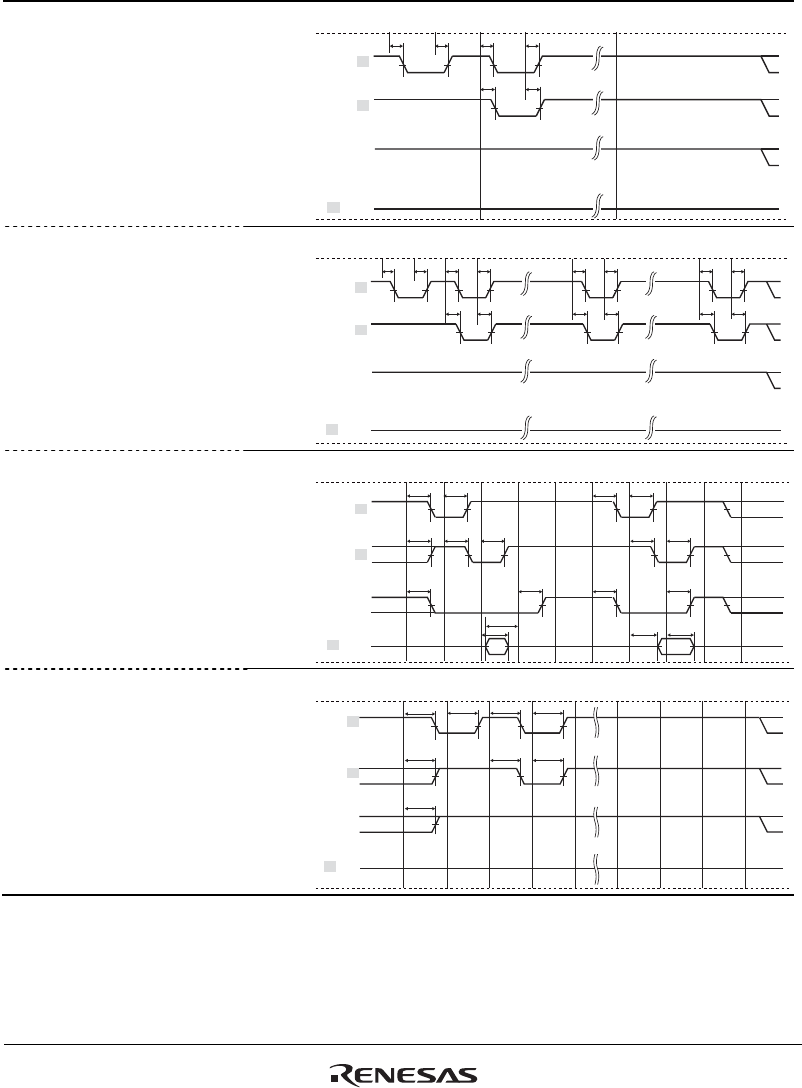

37.4.3 Bus Timing

Figure 37.32 Synchronous

DRAM Self-Refreshing

Timing (WTRP = 1 Cycle)

2007 Figure amended

t

RASD1

t

RASD1

t

RASD1

t

RASD1

D15 to D0

RAS

t

CASD1

t

CASD1

CAS

(Hi-Z)

DQMxx

Figure 37.33 Synchronous

DRAM Mode Register Write

Timing (WTRP = 1 Cycle)

2008 Figure amended

t

RASD1

t

RASD1

t

RASD1

t

RASD1

D15 to D0

RAS

t

CASD1

t

CASD1

CAS

(Hi-Z)

DQMxx

t

RASD1

t

RASD1

t

CASD1

t

CASD1

t

RASD1

t

RASD1

t

CASD1

t

CASD1

Figure 37.34 Synchronous

DRAM Access Timing in

Low-Frequency Mode

(Auto-Precharge, TRWL = 2

Cycles)

2009 Figure amended

D15 to D0

RAS

CAS

DQMxx

t

CASD2

t

CASD2

t

CASD2

t

CASD2

t

CASD2

t

RASD2

t

RASD2

t

RASD2

t

RASD2

t

DQMD2

t

DQMD2

t

DQMD2

t

DQMD2

t

RDS4

t

RDH4

t

WDD3

t

WDH3

Figure 37.35 Synchronous

DRAM Self-Refreshing

Timing in Low-Frequency

Mode (WTRP = 2 Cycles)

2010 Figure amended

D15 to D0

RAS

CAS

(Hi-Z)

DQMxx

t

CASD2

t

DQMD2

t

CASD2

t

CASD2

t

RASD2

t

RASD2

t

RASD2

t

RASD2