Section 21 IEBus

TM

Controller

Page 1100 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

For use of active low signals, levels are reversed from the active high signals.

The synchronous and data periods have approximately the same length.

The IEBus is synchronized bit by bit. The specifications for the time of all bits and the periods

allocated to the bits differ depending on the type of transfer bits and the unit (master or slave unit).

21.1.5 Configuration

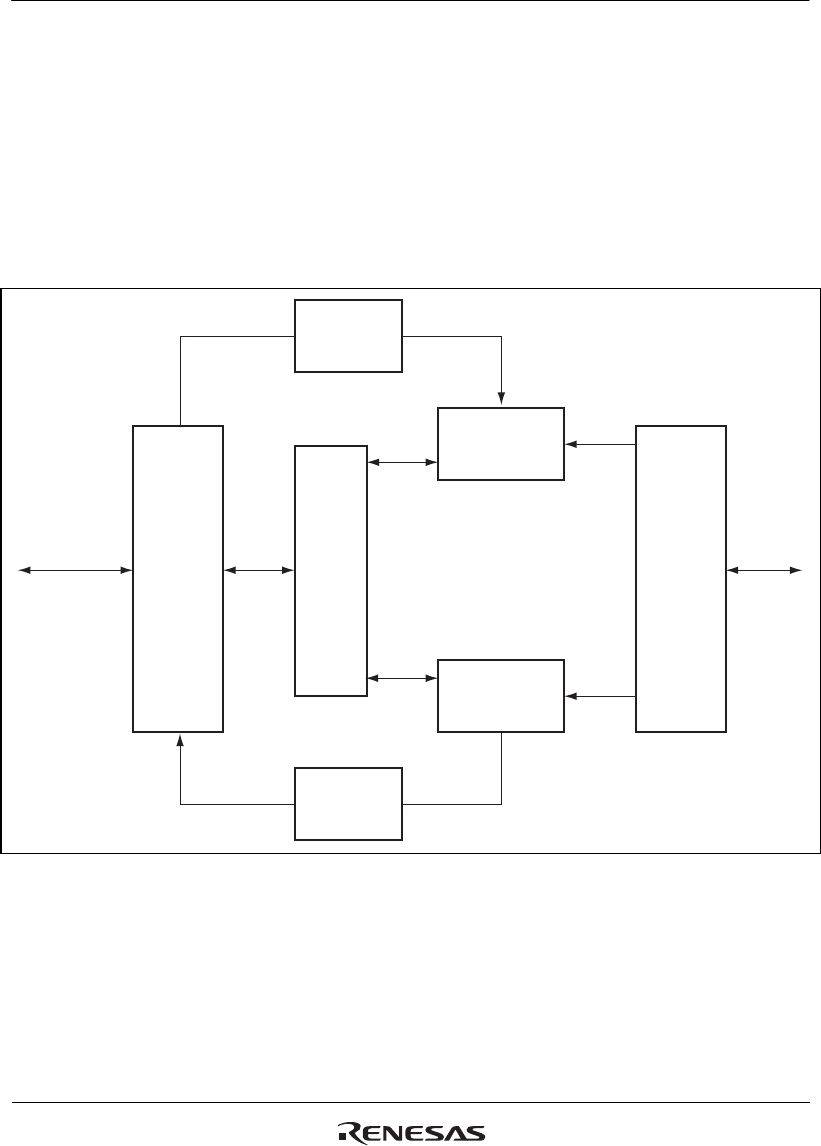

Figure 21.5 shows the entire block configuration and table 21.6 lists the functions of each block.

Transmit

data buffer

Internal

bus

interface

IEBbus

interface

IEBus

Receive

data buffer

Transmit controller

Register

Internal bus

Receive controller

Figure 21.5 Block Diagram