Section 19 Serial I/O with FIFO

Page 970 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

19.4.6 Transmit and Receive Procedures

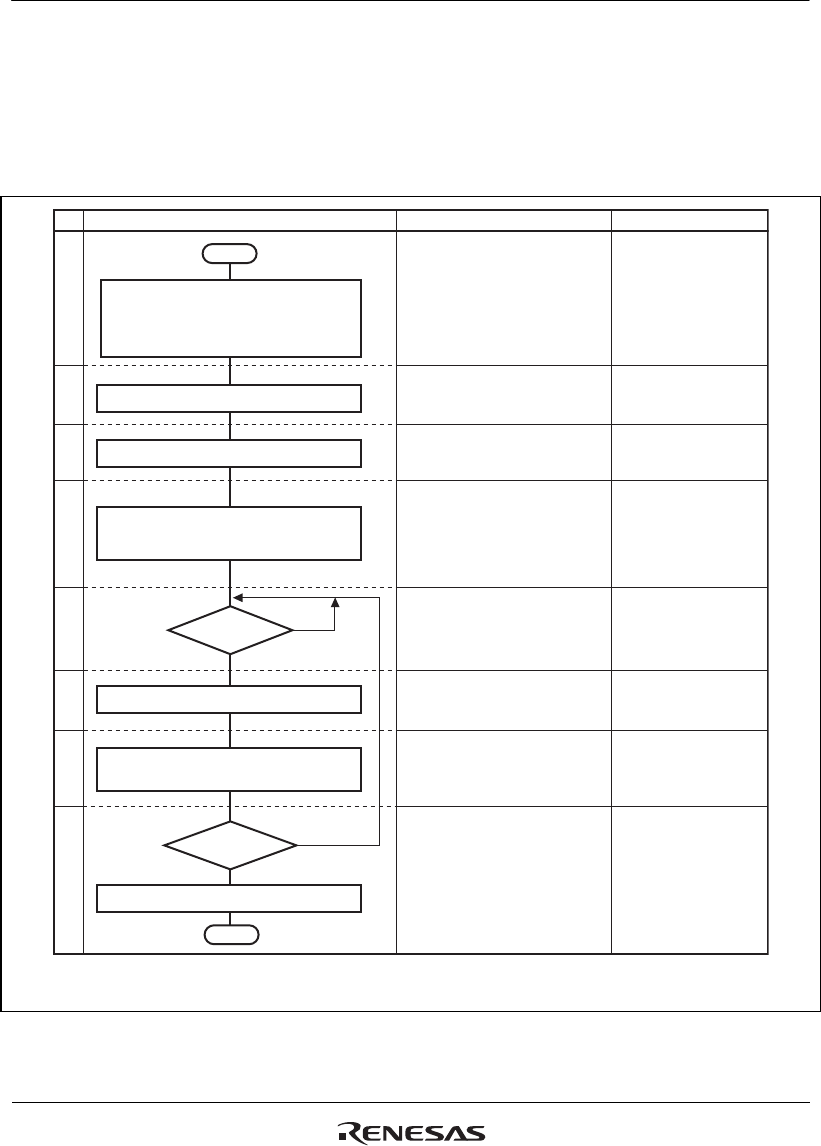

(1) Transmission in Master Mode

Figure 19.6 shows an example of transmission settings and operation when this module is used as

a master.

Start

No

Ye s

No

Ye s

End

No.

1

2

3

4

5

6

7

8

Set SIMDR, SISCR, SITDAR,

and SIFCTR

Set the SCKE bit in SICTR to 1

Start SIOFSCK output

Set the FSE and TXE bits

in SICTR to 1

TDREQ = 1?

Set SITDR

Transmit SITDR from SIOFTXD

synchronously with SIOFSYNC

Transfer

ended?

Clear the TXE bit in SICTR to 0

Set operating mode, serial clock,

slot position for transmit data,

and FIFO request threshold

value

Set operation start for baud rate

generator

Set the start for frame synchronous

signal output and enable

transmission

Set transmit data

Set to disable transmission

Output serial clock

Output frame synchronous

signal and issue transmit

transfer request*

Transmit

End transmission

Flow Chart

Settings of This Module Operation of This Module

Note: * To avoid occurrence of a transmit data underflow, the TXE bit should be set to 1 after setting the no. 6

transmit data,

Figure 19.6 Example of Transmit Operation in Master Mode