Section 25 NAND Flash Memory Controller

Page 1302 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

When ADRMD = 0

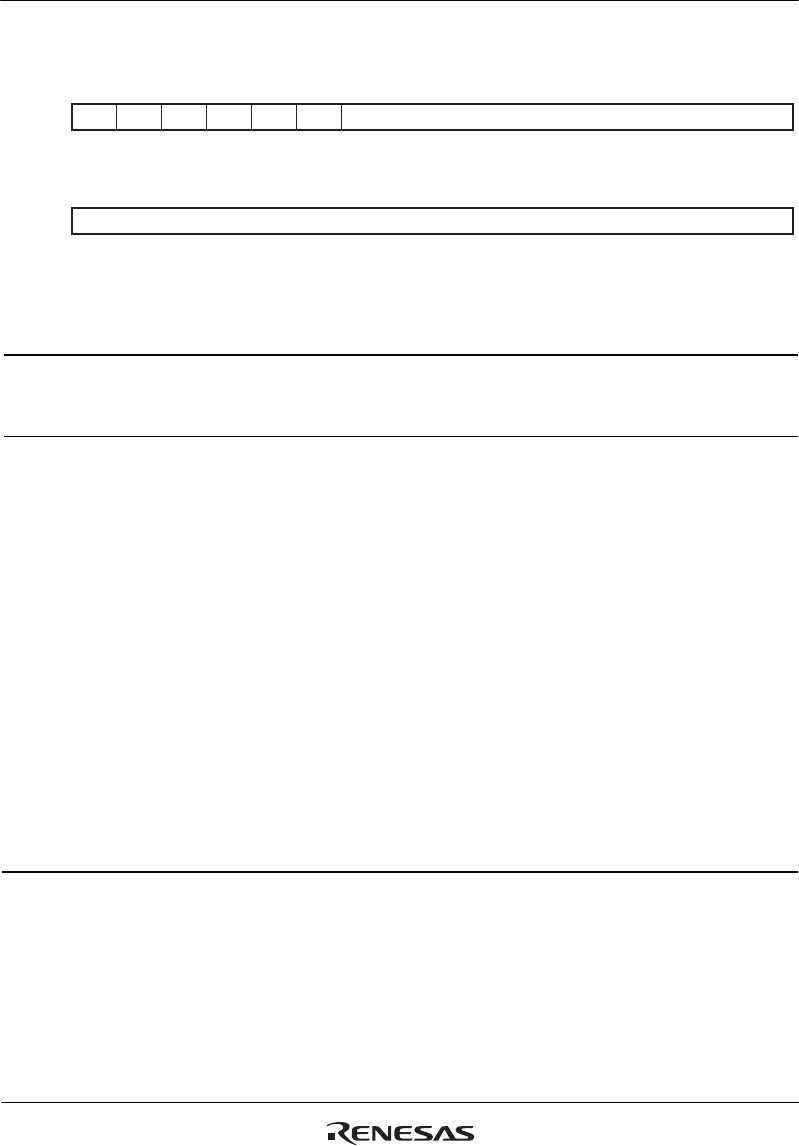

Bit:

Initial value:

R/W:

Bit:

Initial value:

R/W:

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

151413121110987654321

0

0000000000000000

RRRRRRR/WR/WR/WR/WR/WR/WR/WR/WR/WR/W

0000000000000000

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

- - - - - - ADR[25:16]

ADR[15:0]

Bit Bit Name

Initial

Value R/W Description

31 to 26 All 0 R Reserved

These bits are always read as 0. The write value should

always be 0.

25 to 0 ADR[25:0] H'0000 000 R/W Sector Address Specification

Specify a sector number to be accessed when ADRMD

= 0. The sector number is converted into an address

and is output to flash memory.

When the ADRCNT2 bit in FLCMDCR = 1, the

ADR[25:0] bits are valid. When the ADRCNT2 bit in

FLCMDCR = 0, the ADR[17:0] bits are valid. See figure

25.11 for details.

Large-block products (2048 + 64 bytes)

ADR[25:2] specifies the page address and ADR[1:0]

specifies the column address in sector units.

ADR[1:0] = 00: 0th byte (sector 0)

ADR[1:0] = 01: (512 + 16)th byte (sector 1)

ADR[1:0] = 00: (1024 + 32)th byte (sector 2)

ADR[1:0] = 00: (1536 + 48)th byte (sector 3)

Small-block products (512 + 16 bytes)

Only the page address can be specified.