Section 6 Exception Handling

R01UH0134EJ0400 Rev. 4.00 Page 151 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

6.7 When Exception Sources Are Not Accepted

When an address error, FPU exception, register bank error (overflow), or interrupt is generated

immediately after a delayed branch instruction, it is sometimes not accepted immediately but

stored instead, as shown in table 6.11. When this happens, it will be accepted when an instruction

that can accept the exception is decoded.

Table 6.11 Exception Source Generation Immediately after Delayed Branch Instruction

Exception Source

Point of Occurrence

Address

Error

Floating-Point

Unit

Exception

Register Bank

Error (Overflow) Interrupt

Immediately after a delayed

branch instruction

*

Not accepted Not accepted Not accepted Not accepted

Note: * Delayed branch instructions: JMP, JSR, BRA, BSR, RTS, RTE, BF/S, BT/S, BSRF,

BRAF

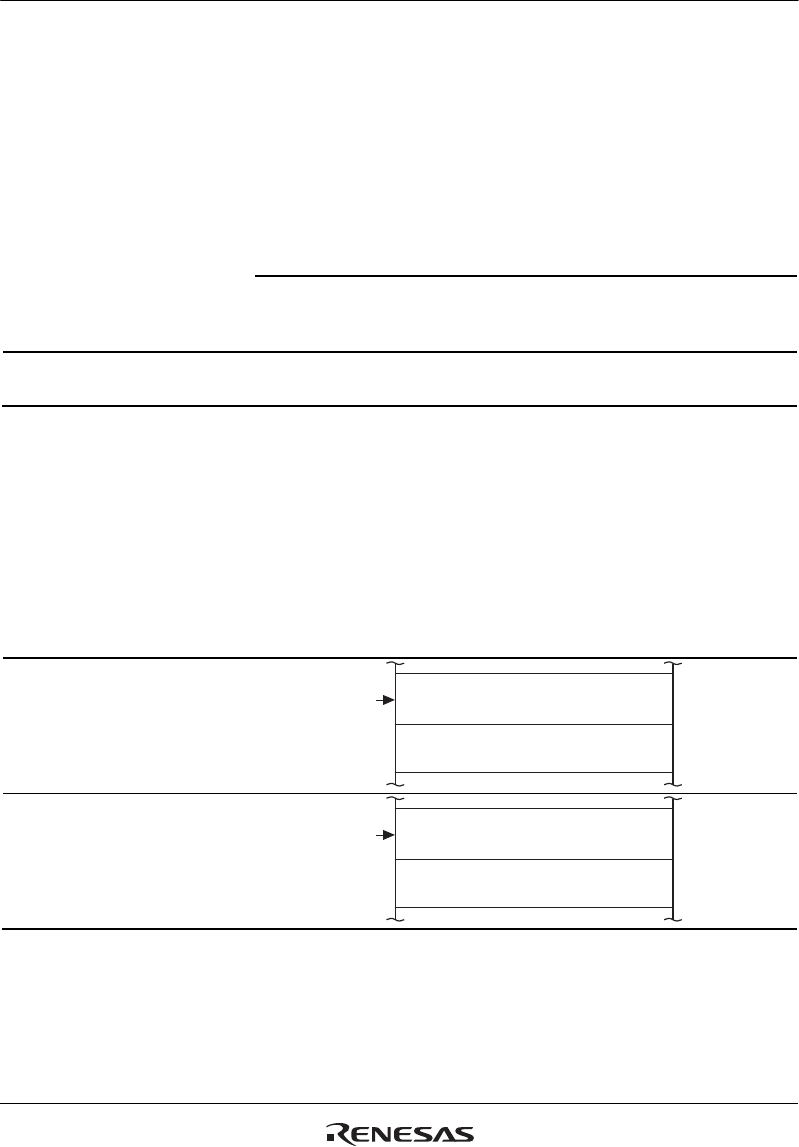

6.8 Stack Status after Exception Handling Ends

The status of the stack after exception handling ends is as shown in table 6.12.

Table 6.12 Stack Status After Exception Handling Ends

Exception Type Stack Status

Address error

32 bits

32 bitsSR

Address of instruction

after executed instruction

SP

Interrupt

32 bits

32 bitsSR

Address of instruction

after executed instruction

SP