Section 10 Direct Memory Access Controller

R01UH0134EJ0400 Rev. 4.00 Page 413 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

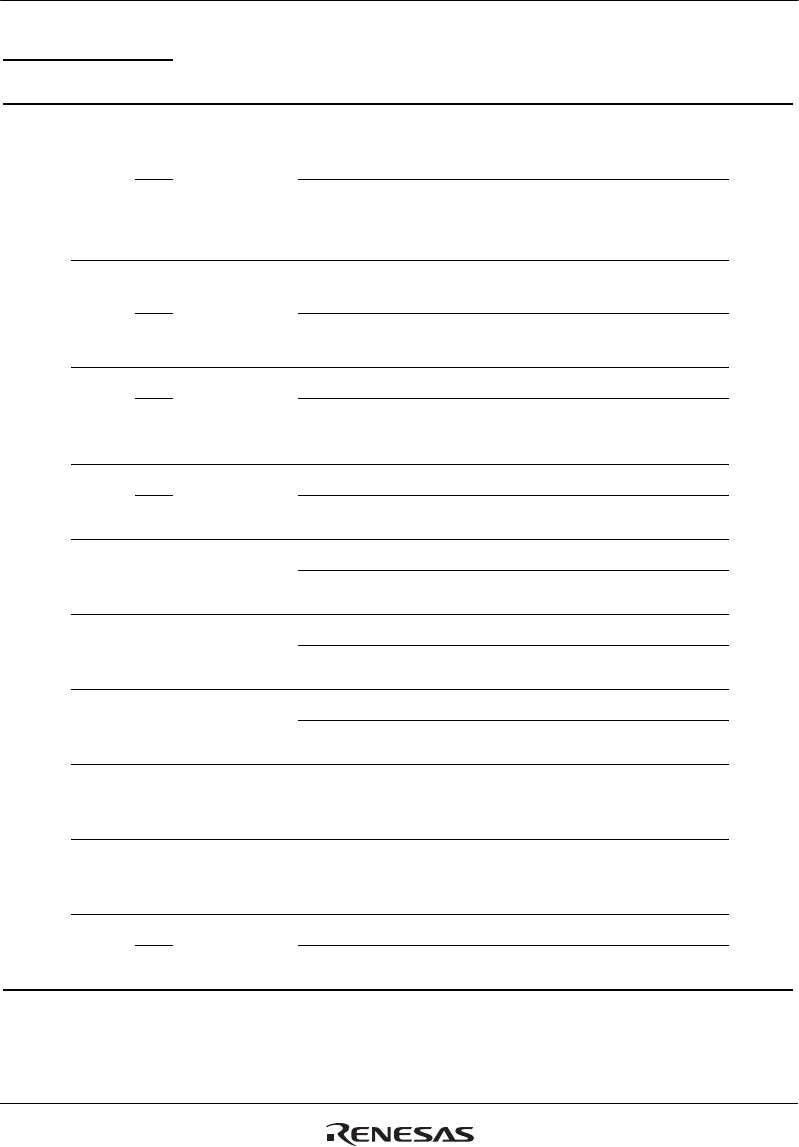

CHCR DMARS DMA Transfer

Request

Source

DMA Transfer Request Signal

Transfer

Source

Transfer

Destination

Bus

Mode

RS[3:0] MID RID

1000 000010 01 Renesas SPDIF

interface

SPDIFTXI

(DMA transfer from transmission

module)

Any TDAD Cycle

steal

10 SPDIFRXI

(DMA transfer to reception

module)

RDAD Any

000100 01 SD host

interface

SD_BUF write Any Data

register

10 SD_BUF read Data

register

Any

000110 01 Clock

synchronous

serial I/O with

FIFO

TXI transmit data transfer) Any SITDR

10 RXI (receive data transfer) SIRDR Any

001000 01 Serial sound

interface

Channel 0

SSITXI0 (transmit data empty) Any SSIFTDR_0

10 SSIRXI0 (receive data full) SSIFRDR_0 Any

001001 11 Serial sound

interface

Channel 1

SSIRTI1 (transmit data empty) Any SSIFTDR_1

SSIRTI1 (receive data full) SSIFRDR_1 Any

001010 11 Serial sound

interface

Channel 2

SSIRTI2 (transmit data empty) Any SSIFTDR_2

SSIRTI2 (receive data full) SSIFRDR_2 Any

001011 11 Serial sound

interface

Channel 3

SSIRTI3 (transmit data empty) Any SSIFTDR_3

SSIRTI3 (receive data full) SSIFRDR_3 Any

001100 11 Motor control

PWM timer

Channel 1

CMI1 (PWM compare match) Any PWBFR1

001101 11 Motor control

PWM timer

Channel 2

CMI2 (PWM compare match) Any PWBFR2

010000 01 Sampling rate

converter

Channel 0

IDEI0 (input data empty) Any SRCIDR_0

10 ODFI0 (output data full) SRCODR_0 Any