Section 7 Interrupt Controller

Page 202 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

7.8.1 Banked Register and Input/Output of Banks

(1) Banked Register

The contents of the general registers (R0 to R14), global base register (GBR), multiply and

accumulate registers (MACH and MACL), and procedure register (PR), and the vector table

address offset are banked.

(2) Input/Output of Banks

This LSI has fifteen register banks, bank 0 to bank 14. Register banks are stacked in first-in last-

out (FILO) sequence. Saving takes place in order, beginning from bank 0, and restoration takes

place in the reverse order, beginning from the last bank saved to.

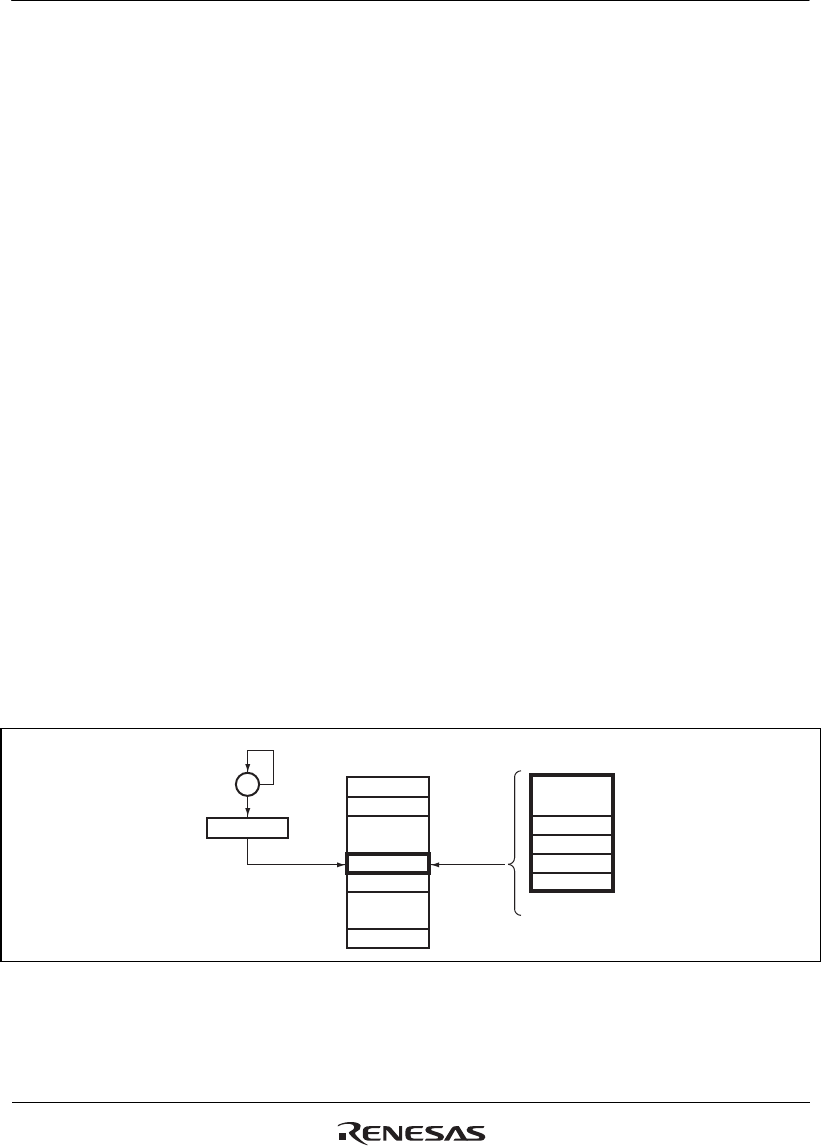

7.8.2 Bank Save and Restore Operations

(1) Saving to Bank

Figure 7.11 shows register bank save operations. The following operations are performed when an

interrupt for which usage of register banks is allowed is accepted by the CPU:

a. Assume that the bank number bit value in the bank number register (IBNR), BN, is i before the

interrupt is generated.

b. The contents of registers R0 to R14, GBR, MACH, MACL, and PR, and the interrupt vector

table address offset (VTO) of the accepted interrupt are saved in the bank indicated by BN,

bank i.

c. The BN value is incremented by 1.

Bank 0

Register banks Registers

Bank 1

:

:

:

:

Bank i

Bank i + 1

Bank 14

+1

(a)

(c)

(b)

BN

GBR

MACH

MACL

PR

VTO

R0 to R14

Figure 7.11 Bank Save Operations