Section 16 Renesas Serial Peripheral Interface

Page 838 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

(g) Next-Access Delay (t3)

The next-access delay value in master mode depends on SPNDEN bit settings in the command

register (SPCMD) and on next-access delay register (SPND) settings. This module determines the

SPCMD to be referenced during serial transfer by pointer control, and determines a next-access

delay value during serial transfer by using the SPNDEN bit in the selected SPCMD and SPND, as

shown in table 16.10. For a definition of next-access delay, see section 16.4.4, Transfer Format.

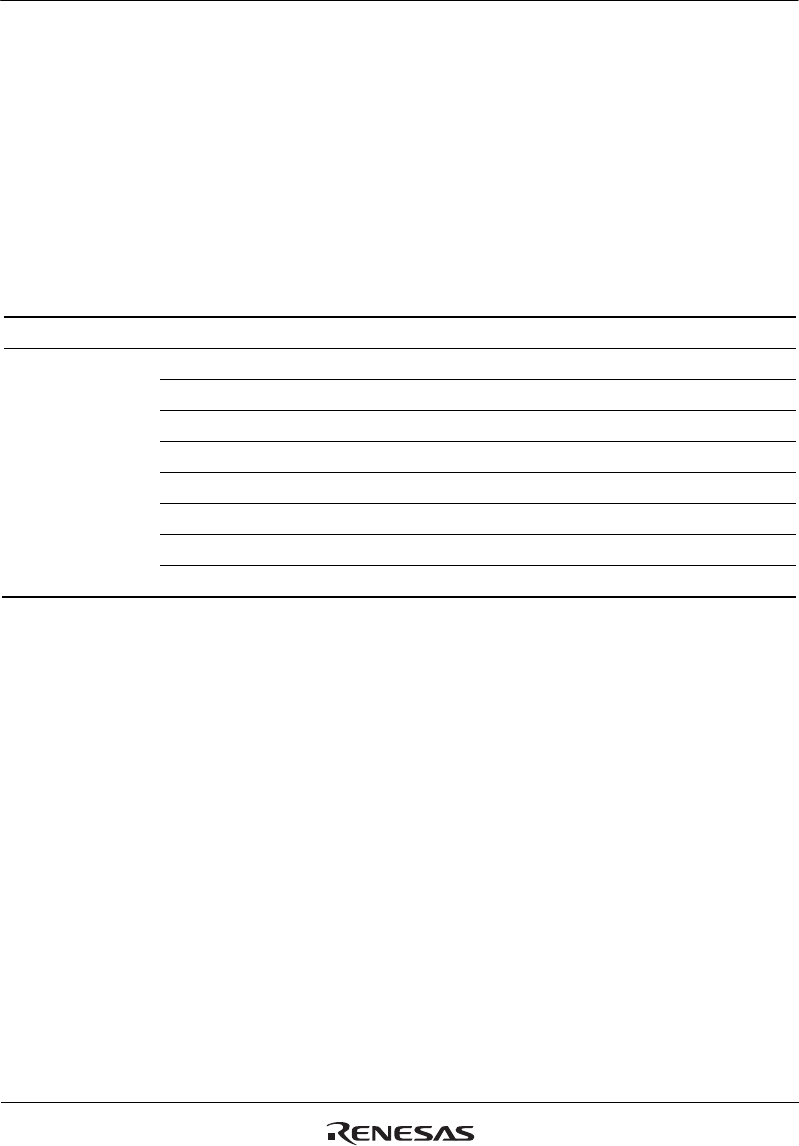

Table 16.10 Relationship among SPNDEN and SPND Settings and Next-Access Delay

Values

SPNDEN SPND Next-Access Delay Value

0 000 to 111 1 RSPCK 2 B

1 000 1 RSPCK 2 B

001 2 RSPCK 2 B

010 3 RSPCK 2 B

011 4 RSPCK 2 B

100 5 RSPCK 2 B

101 6 RSPCK 2 B

110 7 RSPCK 2 B

111 8 RSPCK 2 B

(h) Initialization Flowchart

Figure 16.17 is a flowchart illustrating an example of initialization in SPI operation when this

module is used in master mode. For a description of how to set up the interrupt controller, direct

memory access controller, and input/output ports, see the descriptions given in the individual

blocks.