Section 2 CPU

R01UH0134EJ0400 Rev. 4.00 Page 89 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

Instruction Instruction Code Operation

Execu-

tion

Cycles

T Bit

Compatibility

SH2E SH4

SH-2A/

SH2A-

FPU

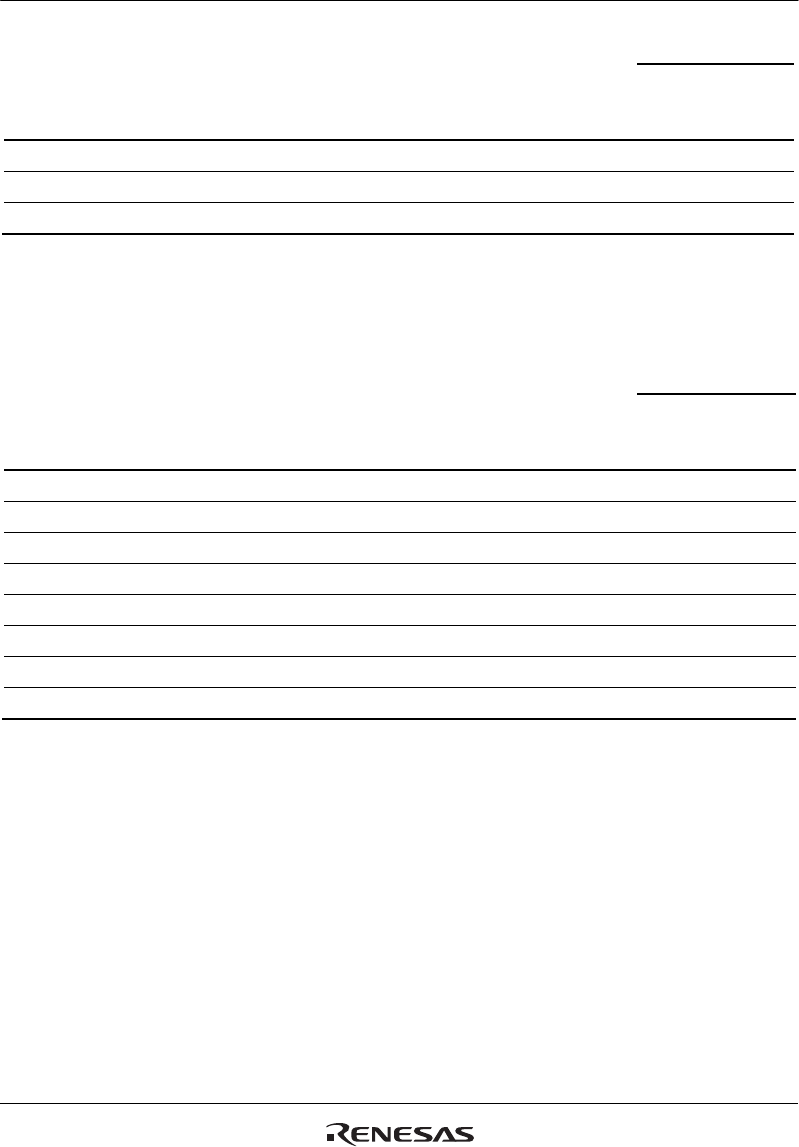

FSUB DRm, DRn 1111nnn0mmm00001 DRn-DRm DRn 6 Yes Yes

FTRC FRm, FPUL 1111mmmm00111101 (long)FRm FPUL 1 Yes Yes Yes

FTRC DRm, FPUL 1111mmm000111101 (long)DRm FPUL 2 Yes Yes

2.4.9 FPU-Related CPU Instructions

Table 2.18 FPU-Related CPU Instructions

Instruction Instruction Code Operation

Execu-

tion

Cycles

T Bit

Compatibility

SH2E SH4

SH-2A/

SH2A-

FPU

LDS Rm,FPSCR 0100mmmm01101010 Rm FPSCR 1 Yes Yes Yes

LDS Rm,FPUL 0100mmmm01011010 Rm FPUL 1 Yes Yes Yes

LDS.L @Rm+, FPSCR 0100mmmm01100110 (Rm) FPSCR, Rm+=4 1 Yes Yes Yes

LDS.L @Rm+, FPUL 0100mmmm01010110 (Rm) FPUL, Rm+=4 1 Yes Yes Yes

STS FPSCR, Rn 0000nnnn01101010 FPSCR Rn 1 Yes Yes Yes

STS FPUL,Rn 0000nnnn01011010 FPUL Rn 1 Yes Yes Yes

STS.L FPSCR,@-Rn 0100nnnn01100010 Rn-=4, FPCSR (Rn) 1 Yes Yes Yes

STS.L FPUL,@-Rn 0100nnnn01010010 Rn-=4, FPUL (Rn) 1 Yes Yes Yes