Section 16 Renesas Serial Peripheral Interface

R01UH0134EJ0400 Rev. 4.00 Page 835 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

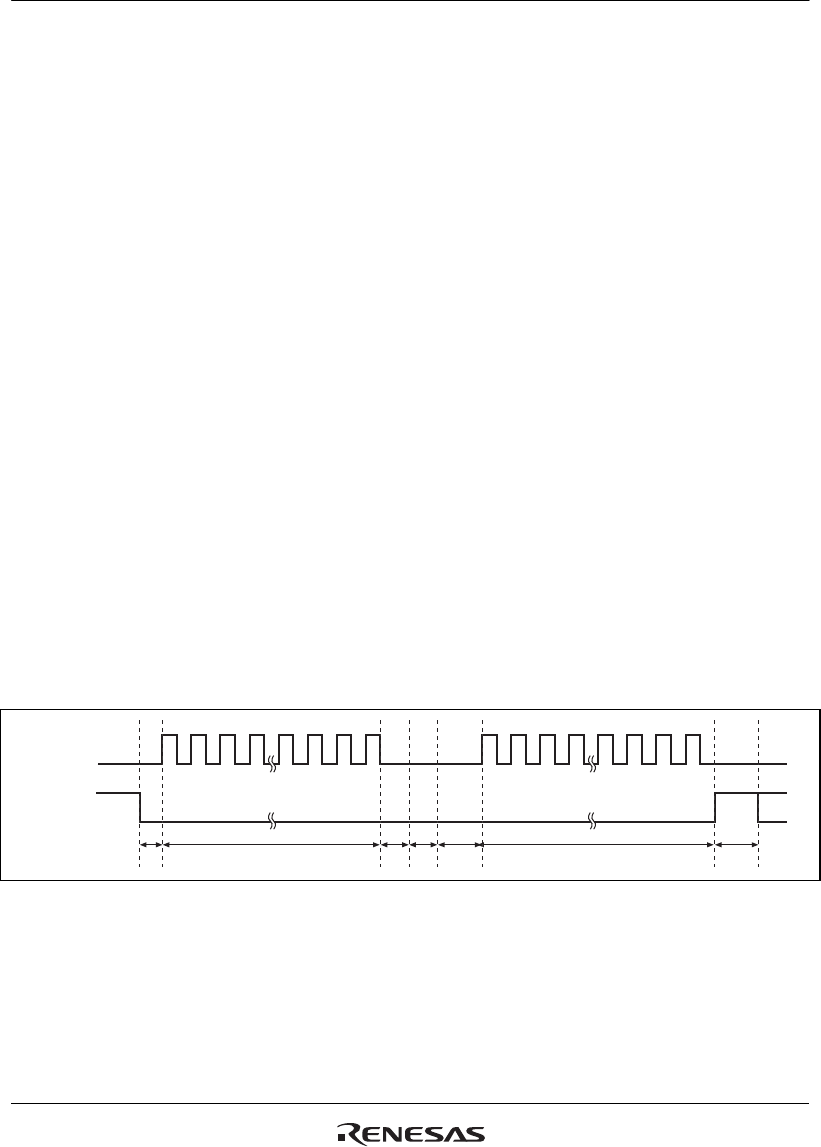

(d) Burst Transfer

If the SSLKP bit in the command register (SPCMD) that this module references during the current

serial transfer is 1, this module keeps the SSL signal level during the serial transfer until the

beginning of the SSL signal assertion for the next serial transfer. If the SSL signal level for the

next serial transfer is the same as the SSL signal level for the current serial transfer, this module

can execute continuous serial transfers while keeping the SSL signal assertion status (burst

transfer).

Figure 16.16 shows an example of an SSL signal operation for the case where a burst transfer is

implemented using SPCMD0 and SPCMD1 settings. The text below explains operations (1) to (7)

as depicted in figure 16.16. It should be noted that the polarity of the SSL output signal depends

on the settings in the slave select polarity register (SSLP).

1. Based on SPCMD0, this module asserts the SSL signal and inserts RSPCK delays.

2. Serial transfers are executed according to SPCMD0.

3. SSL negation delays are inserted.

4. Because the SSLKP bit in SPCMD0 is 1, this module keeps the SSL signal value on SPCMD0.

This period is sustained, at the shortest, for a period equal to the next-access delay of

SPCMD0. If the shift register is empty after the passage of a minimum period, this period is

sustained until such time as the transmit data is stored in the shift register for another transfer.

5. Based on SPCMD1, this module asserts the SSL signal and inserts RSPCK delays.

6. Serial transfers are executed according to SPCMD1.

7. Because the SSLKP bit in SPCMD1 is 0, this module negates the SSL signal. In addition, a

next-access delay is inserted according to SPCMD1.

SSL

(1) (2) (3) (4) (5) (6) (7)

RSPCK

(CPHA = 1,

CPOL = 0)

Figure 16.16 Example of Burst Transfer Operation using SSLKP Bit