Section 9 Bus State Controller

Page 354 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

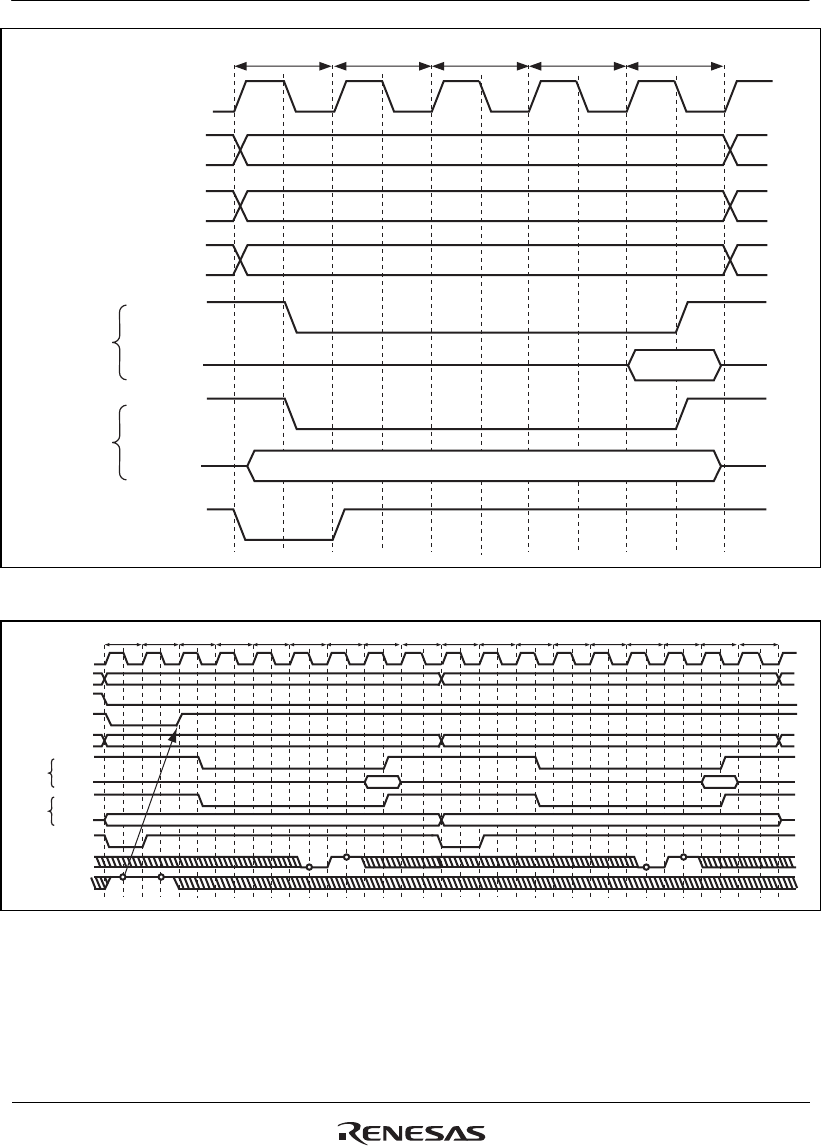

Tpci1w

CKIO

A25 to A0

CExx

RD/WR

ICIORD

D15 to D0

ICIOWR

D15 to D0

BS

Read

Write

Tpci2Tpci1 Tpci1w Tpci1w

Figure 9.42 Basic Access Timing for PCMCIA I/O Card Interface

Tpci1w

CKIO

A25 to A0

CE1x

RD/WR

ICIORD

D15 to D0

ICIOWR

IOIS16

D15 to D0

BS

Read

Write

Tpci2

CE2x

Tpci0 Tpci1

Tpci1wTpci0w Tpci2wTpci1w Tpci1w

WAIT

Tpci1w Tpci2Tpci0 Tpci1 Tpci1wTpci0w Tpci2wTpci1w Tpci1w

Figure 9.43 Dynamic Bus-Size Adjustment Timing for PCMCIA I/O Card Interface

(TED[3:0] = B'0010, PCW[3:0] = B'0000, TEH[3:0] = B'0001, Hardware Wait = 1)