Section 25 NAND Flash Memory Controller

R01UH0134EJ0400 Rev. 4.00 Page 1315 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

25.3.13 Transfer Control Register (FLTRCR)

Setting the TRSTRT bit to 1 initiates access to flash memory. Access completion can be checked

by the TREND bit. During the transfer (from when the TRSTRT bit is set to 1 until the TREND

bit is set to 1), the processing should not be forcibly ended (by setting the TRSTRT bit to 0).

When reading from flash memory, TREND is set when reading from flash memory have been

finished. However, if there is any read data remaining in the FIFO, the processing should not be

forcibly ended until all data has been read from the FIFO. While this module has the external bus

mastership and transfer is in progress, the SLEEP instruction should not be executed until the

TREND bit is set and transfer is completed.

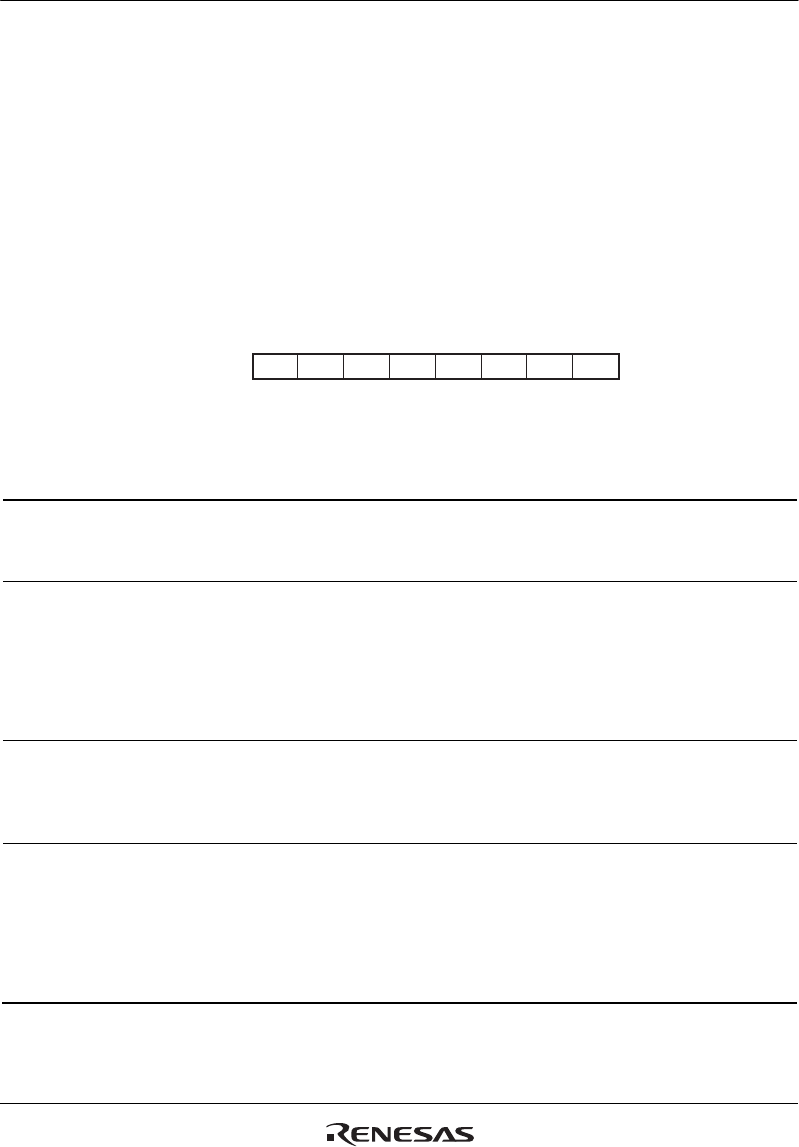

Bit:

Initial value:

R/W:

76543210

00000000

RRRRRRR/WR/W

-----

TR

STAT

TR

END

TR

STRT

Bit Bit Name

Initial

Value R/W Description

7 to 3 All 0 R Reserved

These bits are always read as 0. The write value should

always be 0.

2 TRSTAT 0 R Transfer State

Indicates that this module has acquired the external bus

mastership and that transfer is actually being

performed.

0: Transfer has not been started.

1: Transfer is in progress or transfer has ended.

1 TREND 0 R/W Processing End Flag Bit

Indicates that the processing performed in the specified

access mode has been completed. The write value

should always be 0.

0 TRSTRT 0 R/W Transfer Start

By setting this bit from 0 to 1 when the TREND bit is 0,

processing in the access mode specified by the access

mode specification bits ACM[1:0] is initiated.

0: Stops transfer

1: Starts transfer