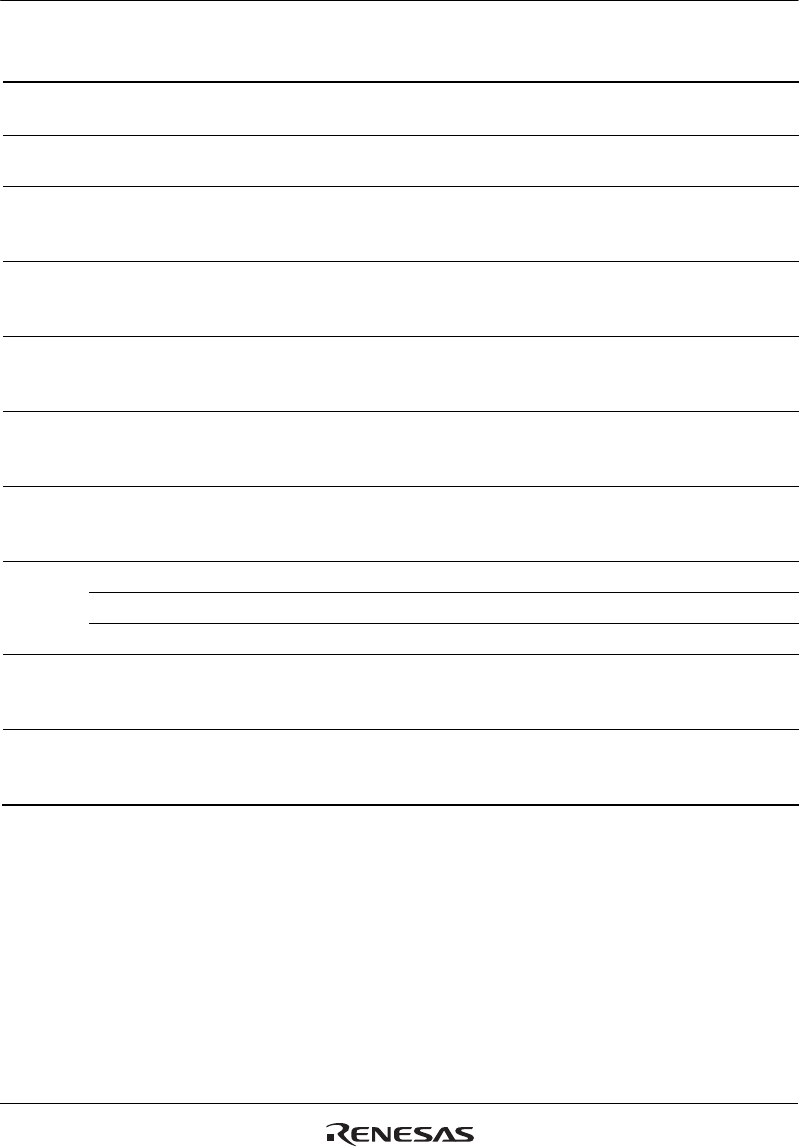

Section 36 List of Registers

R01UH0134EJ0400 Rev. 4.00 Page 1959 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

Module

Name

Register

Abbreviation

Power-On

Reset

Manual

Reset

Deep

Standby

Software

Standby

Module

Standby Sleep

CD-ROM

decoder

All registers Initialized Retained Initialized Retained Retained Retained

A/D

converter

All registers Initialized Retained Initialized Initialized Initialized Retained

NAND flash

memory

controller

All registers Initialized Retained Initialized Retained Retained Retained

USB 2.0

host/func-

tion module

All registers Initialized Retained Initialized Retained Retained Retained

Video

display

controller 3

All registers Initialized Retained Initialized Retained Retained Retained

Sampling

rate

converter

All registers Initialized Retained Initialized Retained Retained Retained

General

purpose I/O

ports

All registers Initialized Retained Initialized Retained Retained

Power-down

modes

DSFR Initialized Retained Retained Retained Retained

XTALCTR Initialized*

10

Retained Retained*

9

Retained*

9

Retained

Other than above Initialized Retained Initialized Retained Retained

User

debugging

interface*

8

SDIR Retained Retained Initialized Retained Retained Retained

Motor

control

PWM timer

All registers Initialized Retained Initialized Retained Retained Retained

Notes: 1. Retains the previous value after an internal power-on reset by means of the watchdog

timer.

2. The BN3 to BN0 bits are initialized.

3. Flag handling continues.

4. Counting up continues.

5. Bits RTCEN and START are retained.

6. Bits BC2 to BC0 are initialized.

7. Transfer operations can be continued.

8. Initialized by TRST assertion or in the Test-Logic-Reset state of the TAP controller.

9. Initialized when realtime clock is not using EXTAL.