Section 2 CPU

Page 82 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

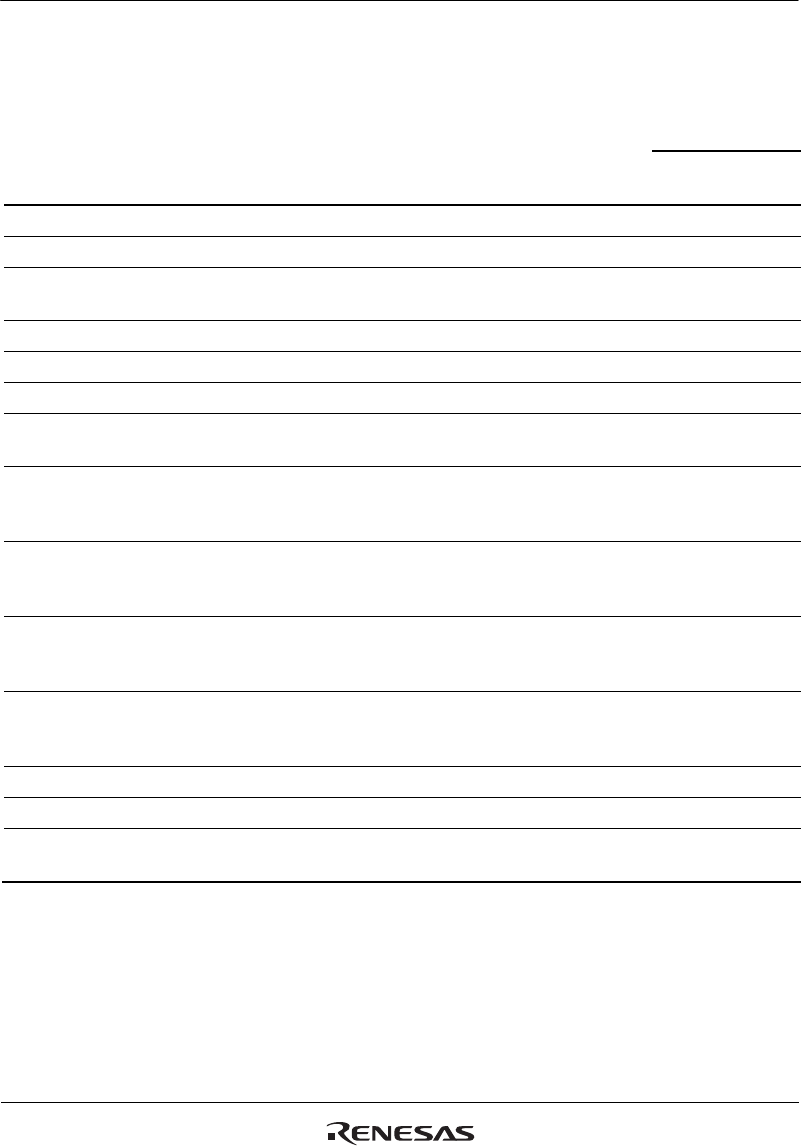

2.4.4 Logic Operation Instructions

Table 2.13 Logic Operation Instructions

Instruction Instruction Code Operation

Execu-

tion

Cycles

T Bit

Compatibility

SH2,

SH2E

SH4 SH-2A

AND Rm,Rn 0010nnnnmmmm1001 Rn & Rm Rn 1 Yes Yes Yes

AND #imm,R0 11001001iiiiiiii R0 & imm R0 1 Yes Yes Yes

AND.B #imm,@(R0,GBR) 11001101iiiiiiii (R0 + GBR) & imm

(R0 + GBR)

3 Yes Yes Yes

NOT Rm,Rn 0110nnnnmmmm0111 ~Rm Rn 1 Yes Yes Yes

OR Rm,Rn 0010nnnnmmmm1011 Rn | Rm Rn 1 Yes Yes Yes

OR #imm,R0 11001011iiiiiiii R0 | imm R0 1 Yes Yes Yes

OR.B #imm,@(R0,GBR) 11001111iiiiiiii (R0 + GBR) | imm

(R0 + GBR)

3 Yes Yes Yes

TAS.B @Rn 0100nnnn00011011 When (Rn) is 0, 1 T

Otherwise, 0 T,

1 MSB of(Rn)

3 Test

result

Yes Yes Yes

TST Rm,Rn 0010nnnnmmmm1000 Rn & Rm

When the result is 0, 1 T

Otherwise, 0 T

1 Test

result

Yes Yes Yes

TST #imm,R0 11001000iiiiiiii R0 & imm

When the result is 0, 1 T

Otherwise, 0 T

1 Test

result

Yes Yes Yes

TST.B #imm,@(R0,GBR) 11001100iiiiiiii (R0 + GBR) & imm

When the result is 0, 1 T

Otherwise, 0 T

3 Test

result

Yes Yes Yes

XOR Rm,Rn 0010nnnnmmmm1010 Rn ^ Rm Rn 1 Yes Yes Yes

XOR #imm,R0 11001010iiiiiiii R0 ^ imm R0 1 Yes Yes Yes

XOR.B #imm,@(R0,GBR) 11001110iiiiiiii (R0 + GBR) ^ imm

(R0 + GBR)

3 Yes Yes Yes