Section 28 Sampling Rate Converter

Page 1638 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

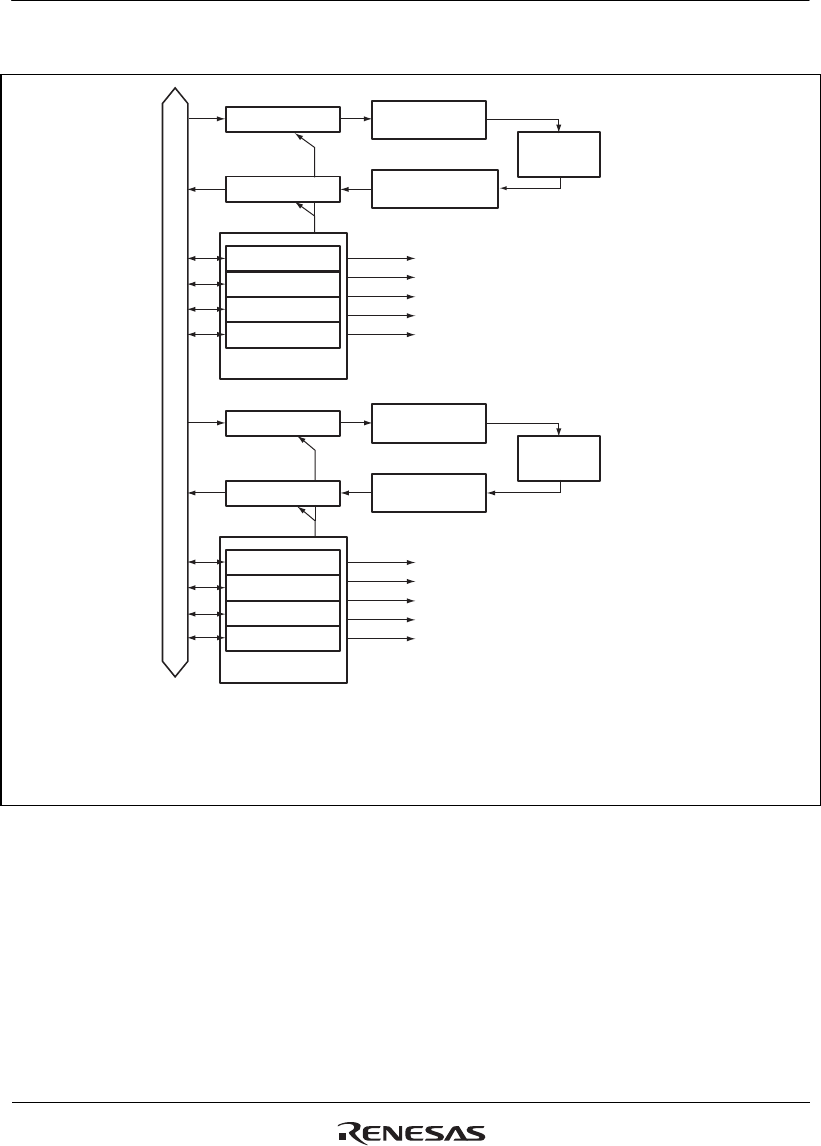

Figure 28.1 shows a block diagram.

SRCID_0

SRCIDCTR

L_0

SRCCTRL_0

SRCODCTRL_0

SRCSTA

T_0

SRCOD_0

SRCID_1

SRCIDCTR

L_1

SRCCTRL_1

SRCODCTRL_1

SRCSTA

T_1

SRCOD_1

Peripheral bus

Input data FIFO

32 bits x 8 stages

Output data FIFO

16 bits x 16 stages

Input data FIFO

16 bits x 8 stages

Output data FIFO

16 bits x 4 stages

FIR filter

FIR filter

Interrupt/DMA transfer request

Interrupt/DMA transfer request

I/O controller

I/O controller

[Legend]

SRCID Input data register

SRCOD Output data register

SRCIDCTRL Input data control register

SRCODCTRL Output data control register

SRCCTRL Control register

SRCSTAT Status register

Figure 28.1 Block Diagram