Section 2 CPU

Page 60 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

2.3.2 Addressing Modes

Addressing modes and effective address calculation are as follows:

Table 2.8 Addressing Modes and Effective Addresses

Addressing

Mode

Instruction

Format

Effective Address Calculation

Equation

Register direct Rn The effective address is register Rn. (The operand

is the contents of register Rn.)

Register indirect @Rn The effective address is the contents of register Rn.

Rn Rn

Rn

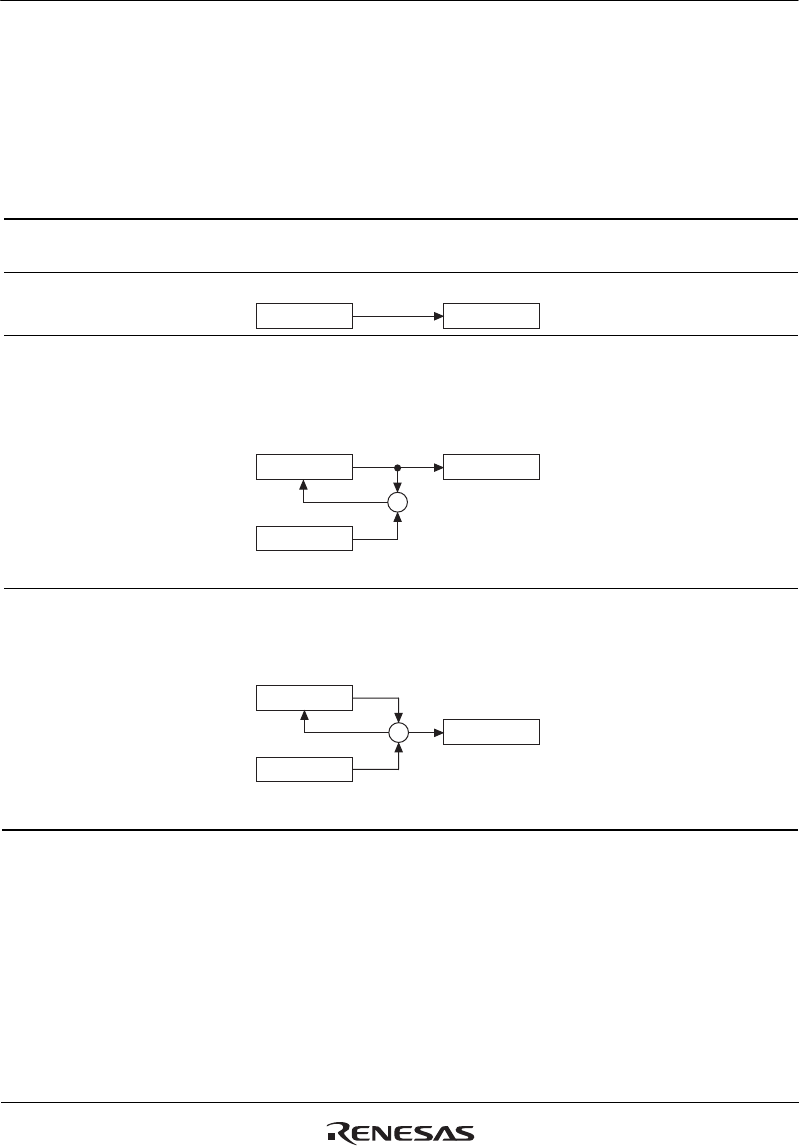

Register indirect

with post-

increment

@Rn+ The effective address is the contents of register Rn.

A constant is added to the contents of Rn after the

instruction is executed. 1 is added for a byte

operation, 2 for a word operation, and 4 for a

longword operation.

Rn Rn

1/2/4

+

Rn + 1/2/4

Rn

(After

instruction

execution)

Byte:

Rn + 1 Rn

Word:

Rn + 2 Rn

Longword:

Rn + 4 Rn

Register indirect

with pre-

decrement

@-Rn The effective address is the value obtained by

subtracting a constant from Rn. 1 is subtracted for

a byte operation, 2 for a word operation, and 4 for

a longword operation.

Rn

1/2/4

Rn – 1/2/4

–

Rn – 1/2/4

Byte:

Rn – 1 Rn

Word:

Rn – 2 Rn

Longword:

Rn – 4 Rn

(Instruction is

executed with

Rn after this

calculation)