Section 11 Multi-Function Timer Pulse Unit 2

R01UH0134EJ0400 Rev. 4.00 Page 477 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

11.3.8 Timer A/D Converter Start Request Control Register (TADCR)

TADCR is a 16-bit readable/writable register that enables or disables A/D converter start requests

and specifies whether to link A/D converter start requests with interrupt skipping operation. This

module has one TADCR in channel 4.

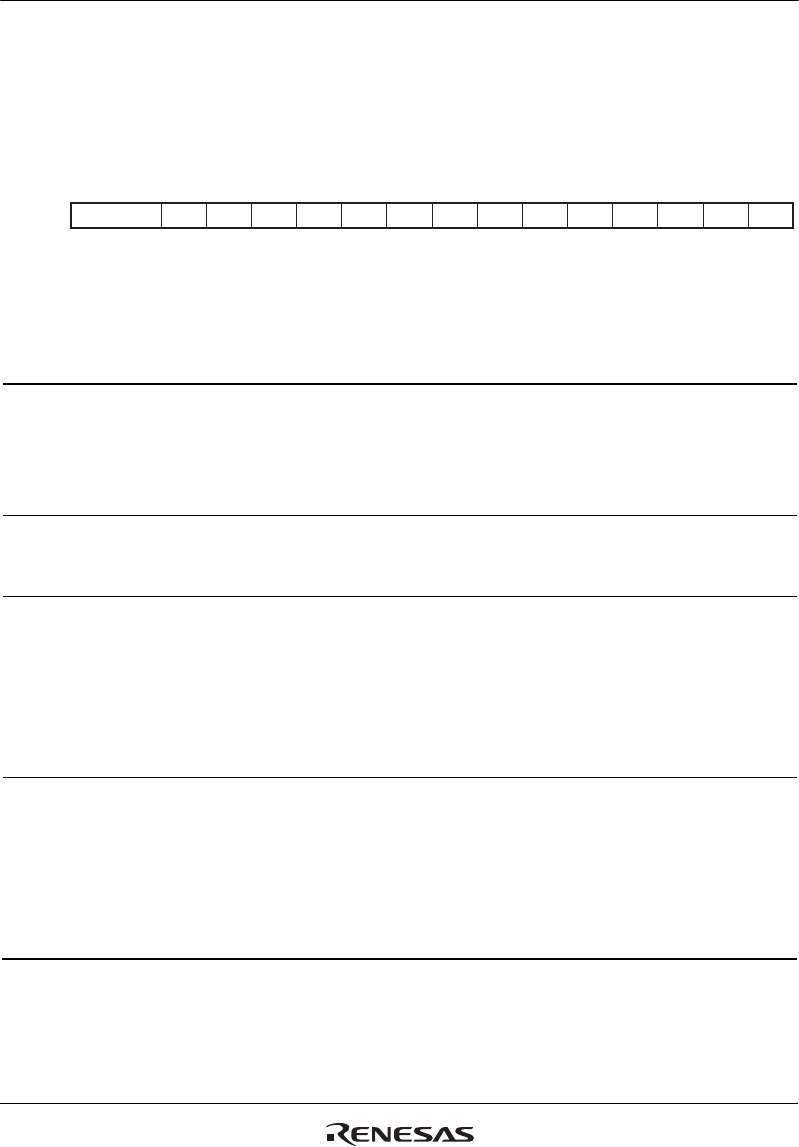

Bit:

Initial value:

R/W:

151413121110987654321

0

0000000000* 00* 0* 0* 0* 0*

R/W R/W R R R R R R R/W R/W R/W R/W R/W R/W R/W R/W

Note: Do not set to 1 when complementary PWM mode is not selected.*

BF[1:0] - - - - - - UT4AE DT4AE UT4BE DT4BE ITA3AE ITA4VE ITB3AE ITB4VE

Bit Bit Name

Initial

Value

R/W Description

15, 14 BF[1:0] 00 R/W TADCOBRA_4/TADCOBRB_4 Transfer Timing Select

Select the timing for transferring data from

TADCOBRA_4 and TADCOBRB_4 to TADCORA_4

and TADCORB_4.

For details, see table 11.27.

13 to 8 All 0 R Reserved

These bits are always read as 0. The write value should

always be 0.

7 UT4AE 0 R/W Up-Count TRG4AN Enable

Enables or disables A/D converter start requests

(TRG4AN) during TCNT_4 up-count operation.

0: A/D converter start requests (TRG4AN) disabled

during TCNT_4 up-count operation

1: A/D converter start requests (TRG4AN) enabled

during TCNT_4 up-count operation

6 DT4AE 0* R/W Down-Count TRG4AN Enable

Enables or disables A/D converter start requests

(TRG4AN) during TCNT_4 down-count operation.

0: A/D converter start requests (TRG4AN) disabled

during TCNT_4 down-count operation

1: A/D converter start requests (TRG4AN) enabled

during TCNT_4 down-count operation