Section 9 Bus State Controller

R01UH0134EJ0400 Rev. 4.00 Page 363 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

Sample Estimation of Idle Cycles between Access Cycles

• Conditions

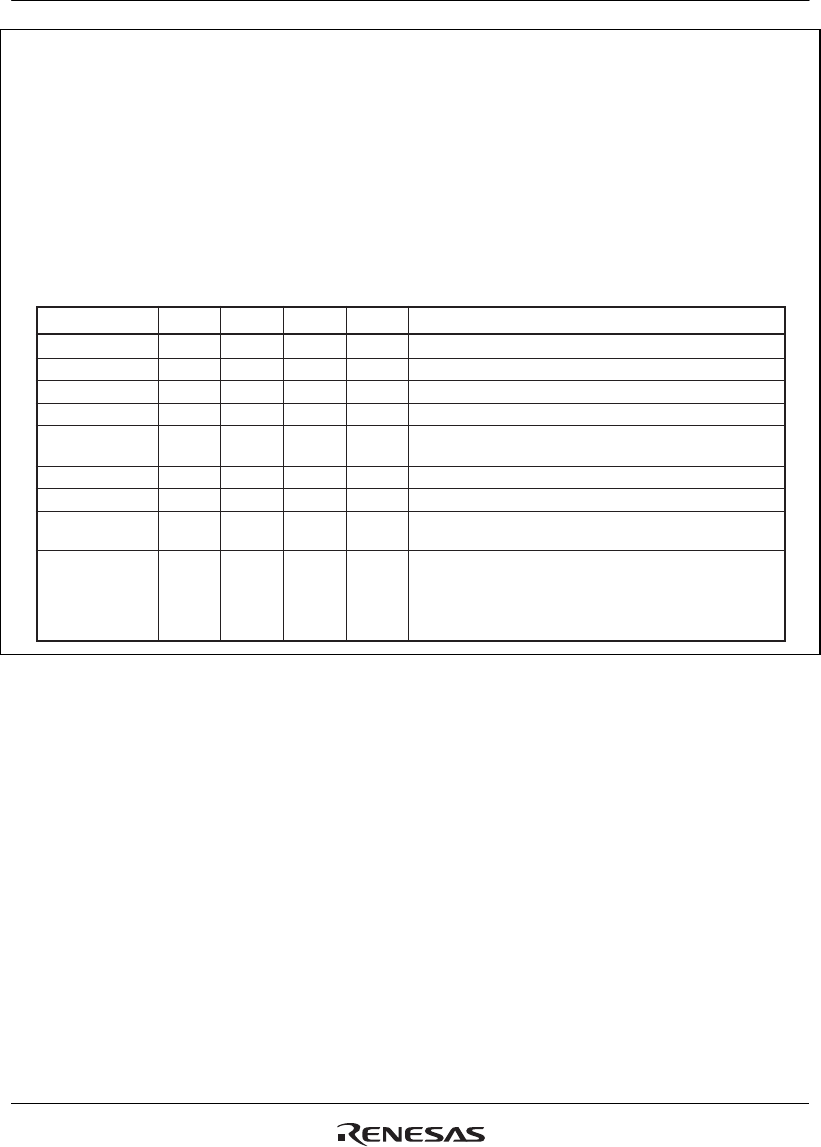

Condition NoteR → RR → WW → WW → R

0000

0000

1100

0220

0100

1420

0000

1420

1

[1] or [2]

[3] or [4]

[5]

[6]

[7]

[5] + [6] + [7]

[8]

Estimated idle

cycles

Actual idle

cycles

CSnBCR is set to 0.

The WM bit is set to 1.

Generated after a read cycle.

See the Iφ:Bφ = 4:1 columns in table 9.17.

No idle cycle is generated for the second time due to the

write buffer effect.

Value for SRAM → SRAM access

Maximum value among conditions [1] or [2], [3] or [4],

[5] + [6] + [7], and [8]

The estimated value does not match the actual value in

the W → R cycles because the internal idle cycles due to

condition [6] is estimated as 0 but actually an internal idle

cycle is generated due to execution of a loop condition

check instruction.

421

The bits for setting the idle cycles between access cycles in CS1BCR and CS2BCR are all set to 0.

In CS1WCR and CS2WCR, the WM bit is set to 1 (external WAIT pin disabled) and the HW[1:0] bits are set to 00

(CS negation is not extended).

Iφ:Bφ is set to 4:1, and no other processing is done during transfer.

For both the CS1 and CS2 spaces, normal SRAM devices are connected, the bus width is 32 bits, and access size is

also 32 bits.

This example estimates the idle cycles for data transfer from the CS1 space to CS2 space by CPU access. Transfer is

repeated in the following order: CS1 read → CS1 read → CS2 write → CS2 write → CS1 read → ...

The idle cycles generated under each condition are estimated for each pair of access cycles. In the following table,

R indicates a read cycle and W indicates a write cycle.

Figure 9.46 Comparison between Estimated Idle Cycles and Actual Value