Section 20 Controller Area Network

R01UH0134EJ0400 Rev. 4.00 Page 987 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

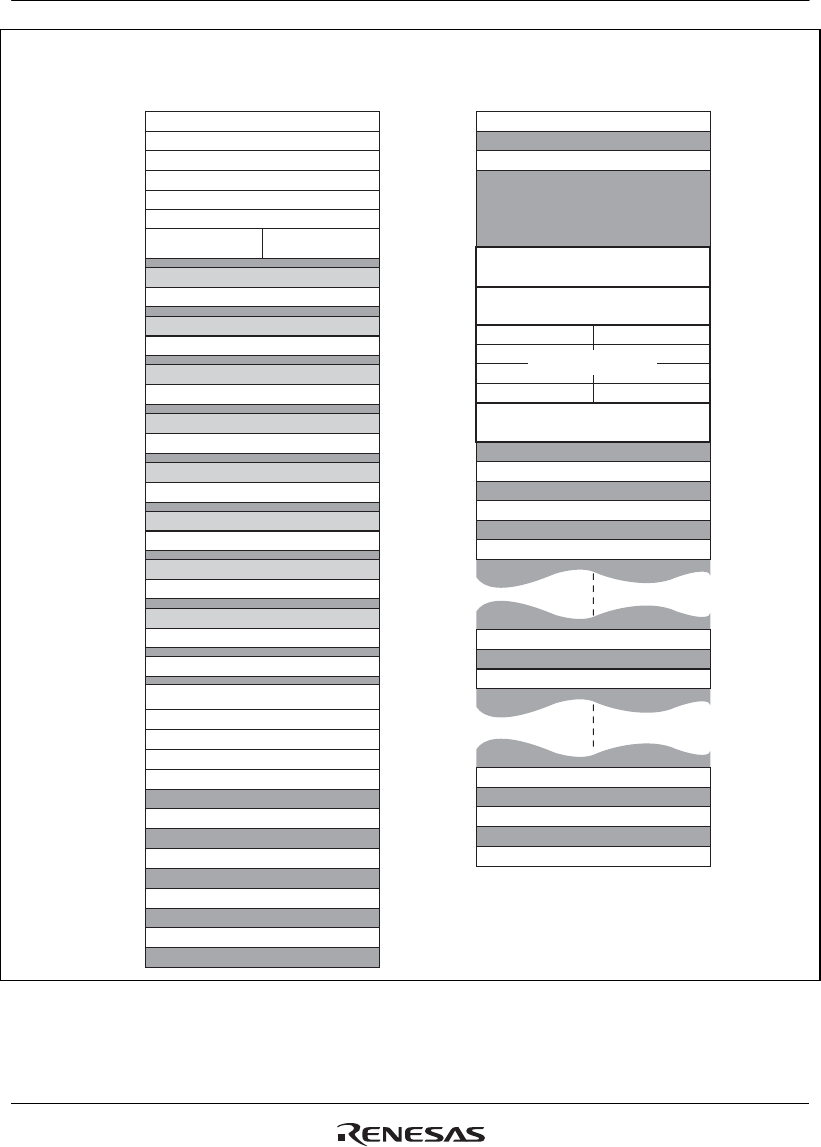

H'000

H'002

H'004

H'006

H'008

H'00A

H'00C

H'020

H'022

H'028

H'02A

H'030

H'032

H'038

H'03A

H'040

H'042

H'048

H'04A

H'050

H'052

H'058

H'05A

H'080

H'082

H'084

H'086

H'088

H'08A

H'08C

H'08E

H'090

H'092

H'094

H'096

H'098

H'09A

H'09C

H'09E

H'0A0

H'0A4

H'100

H'104

H'108

H'10A

H'10C

H'10E

H'110

H'120

H'140

H'160

H'2E0

H'300

H'4A0

H'4C0

H'4E0

LAFM

Bit 15 Bit 0

Master Control Register (MCR)

General Status Register(GSR)

Bit Configuration Register 1 (BCR1)

Bit Configuration Register 0 (BCR0)

Interrupt Request Register (IRR)

Interrupt Mask Register (IMR)

Transmit Pending Register (TXPR1)

Transmit Pending Register (TXPR0)

Transmit Cancel Register (TXCR1)

Transmit Cancel Register (TXCR0)

Transmit Acknowledge Register (TXACK1)

Transmit Acknowledge Register (TXACK0)

Abort Acknowledge Register (ABACK1)

Abort Acknowledge Register (ABACK0)

Receive Pending Register (RXPR1)

Receive Pending Register (RXPR0)

Remote Frame Pending Register (RFPR1)

Remote Frame Pending Register (RFPR0)

Mailbox Interrupt Mask Register (MBIMR1)

Mailbox Interrupt Mask Register (MBIMR0)

Unread Message Status Register (UMSR1)

Unread Message Status Register (UMSR0)

Reference Trigger Offset Register (RFTROFF)

Timer Trigger Control Register0 (TTCR0)

Timer Status Register (TSR)

Timer Compare Match Register 2 (TCMR2)

Tx-Trigger Time Selection Register (TTTSEL)

Cycle Counter Register (CCR)

Cycle Time Register (CYCTR)

Reference Mark Register (RFMK)

Timer Compare Match Register 0 (TCMR0)

Timer Compare Match Register 1 (TCMR1)

Timer Counter Register (TCNTR)

Cycle Maximum/Tx-Enable Window

Register (CMAX_TEW)

Transmit Error

Counter (TEC)

Receive Error

Counter (REC)

Mailbox-0 Control 1 (NMC, MBC, DLC)

Timestamp

Mailbox-1 Control/LAFM/Data etc.

Mailbox 0 Data (8 bytes)

Mailbox-2 Control/LAFM/Data etc.

Mailbox-3 Control/LAFM/Data etc.

Mailbox-15 Control/LAFM/Data etc.

Mailbox-16 Control/LAFM/Data etc.

Mailbox-29 Control/LAFM/Data etc.

Mailbox-30 Control/LAFM/Data etc.

Mailbox-31 Control/LAFM/Data etc.

0

2

4

6

1

3

5

7

Mailbox-0 Control 0

(StdID, ExtID, Rtr, Ide)

Base address

Channel 0: H'FFFE 5000

Channel 1: H'FFFE 5800

Figure 20.2 Memory Map

The locations not used (between H'000 and H'4F3) are reserved and cannot be accessed.