Section 20 Controller Area Network

R01UH0134EJ0400 Rev. 4.00 Page 1017 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

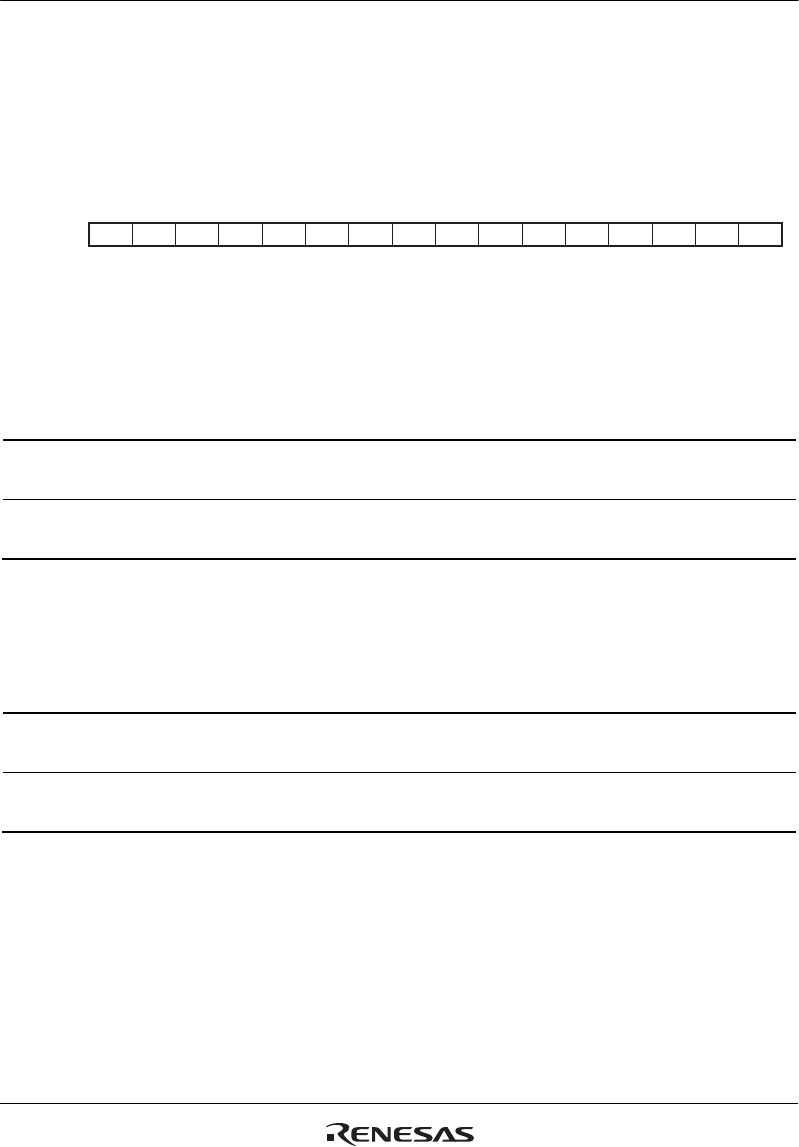

(4) Interrupt Request Register (IRR)

The interrupt request register (IRR) is a 16-bit read/write-clearable register containing status flags

for the various interrupt sources.

IRR (Address = H'008)

1514131211109876543210Bit:

Initial value:

R/W:

0000000000000001

R/W R/W R/W R/W R/W R/W RRR/W R/W R/W R/W R/W RRR/W

IRR15 IRR14 IRR13 IRR12 IRR11 IRR10 IRR9 IRR8 IRR7 IRR6 IRR5 IRR4 IRR3 IRR2 IRR1 IRR0

Bit 15 — Timer Compare Match Interrupt 1 (IRR15): Indicates that a Compare-Match

condition occurred to the Timer Compare Match Register 1 (TCMR1). When the value set in the

TCMR1 matches to Cycle Time (TCMR1 = CYCTR), this bit is set.

Bit 15: IRR15 Description

0 Timer Compare Match has not occurred to the TCMR1 (Initial value)

[Clearing condition] Writing 1

1 Timer Compare Match has occurred to the TCMR1

[Setting condition] TCMR1 matches to Cycle Time (TCMR1 = CYCTR)

Bit 14 — Timer Compare Match Interrupt 0 (IRR14): Indicates that a Compare-Match

condition occurred to the Timer Compare Match Register 0 (TCMR0). When the value set in the

TCMR0 matches to Local Time (TCMR0 = TCNTR), this bit is set.

Bit 14: IRR14 Description

0 Timer Compare Match has not occurred to the TCMR0 (Initial value)

[Clearing condition] Writing 1

1 Timer Compare Match has occurred to the TCMR0

[Setting condition] TCMR0 matches to the Timer value (TCMR0 = TCNTR)

Bit 13 - Timer Overrun Interrupt/Next_is_Gap Reception Interrupt/Message Error

Interrupt (IRR13): This interrupt assumes a different meaning depending on this module mode.

It indicates that:

The Timer (TCNTR) has overrun when this module is working in event-trigger mode

(including test modes)