ADC

ADD WITH CARRY

ADC

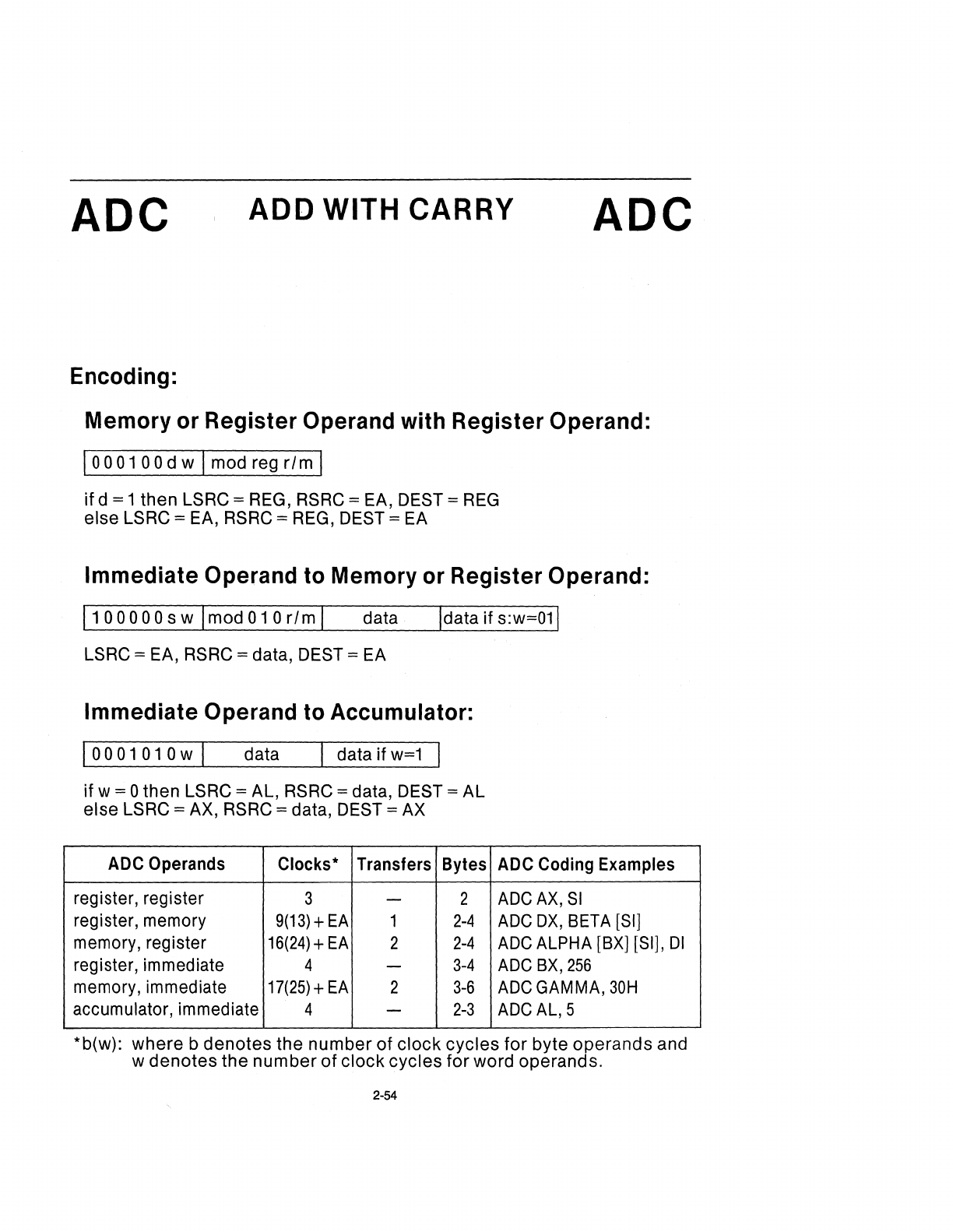

Encoding:

Memory or Register

Operand with Register Operand:

10001

00

d w 1

mod

reg rIm 1

if

d = 1

then

LSRC = REG, RSRC = EA, DEST = REG

else

LSRC = EA, RSRC = REG, DEST = EA

Immediate Operand to Memory or Register Operand:

1100000

s w 1

mod

0 1 0 rIm 1

data

Idata

if

s:w=01!

LSRC

= EA, RSRC = data, DEST = EA

Immediate Operand to Accumulator:

1

00

0 1 0 1 0 w 1 data 1 data

if

w=1 1

if

w = 0

then

LSRC = AL, RSRC = data, DEST =

AL

else

LSRC = AX, RSRC = data, DEST = AX

ADC

Operands

Clocks·

Transfers

Bytes

register, register

3

- 2

register, memory

9(13)+EA 1

2-4

memory, register 16(24)+

EA

2

2-4

register, immediate

4

-

3-4

memory, immediate

17(25)

+

EA

2

3-6

accumulator, immediate 4

-

2-3

ADC

Coding

Examples

ADCAX,

SI

AOC

OX,

BETA [SI]

AOC

ALPHA [BX] [SI],

01

AOC

BX,

256

AOC

GAMMA,

30H

AOC

AL, 5

*b(w):

where

b

denotes

the

number

of

clock

cycles

for

byte

operands

and

w

denotes

the

number

of

clock

cycles

for

word

operands.

2-54