8284A

CLOCK GENERATOR

AND

DRIVER FOR

iAPX 86, 88

PROCESSORS

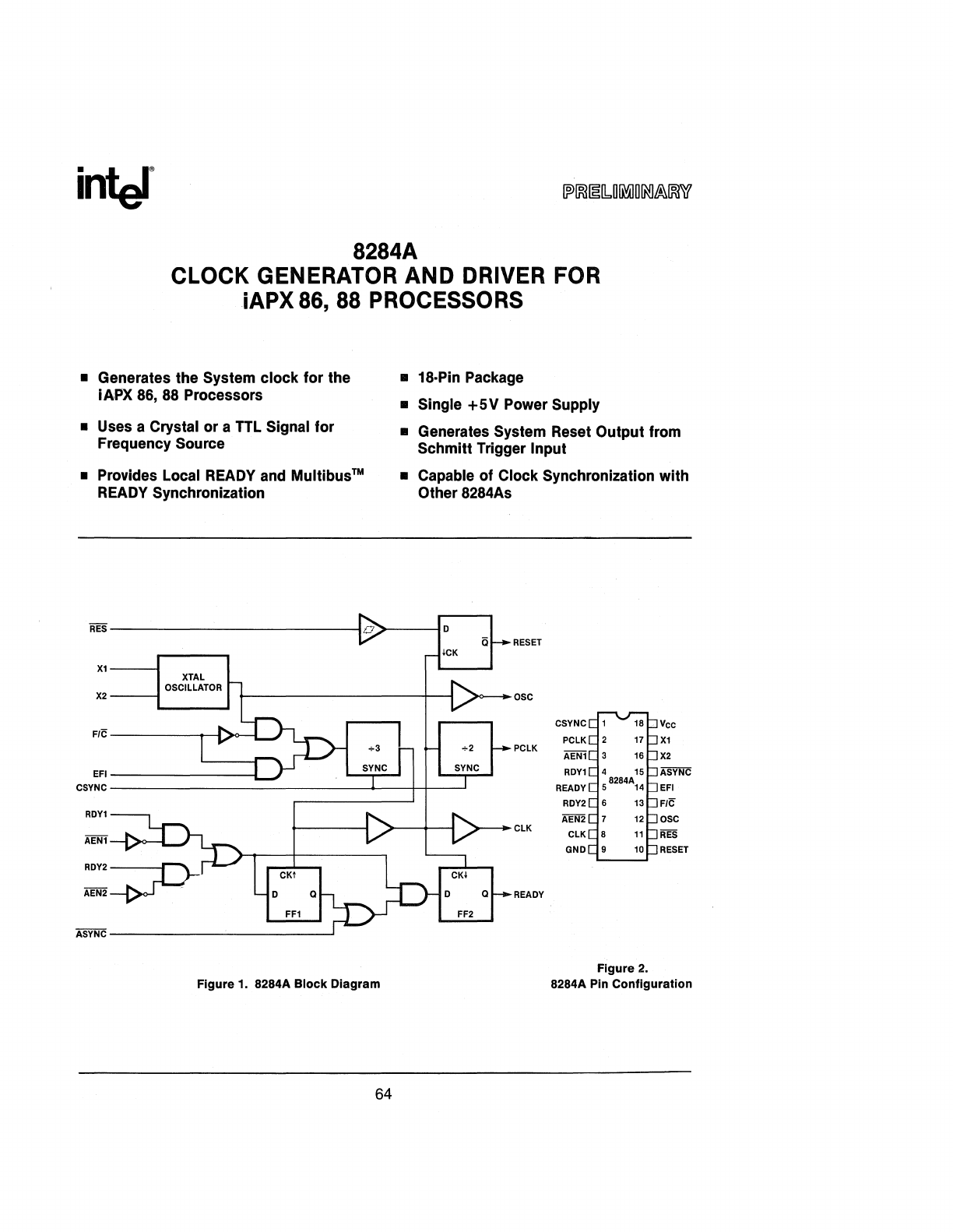

• Generates the System clock for the

iA,PX

86,88

Processors

• Uses a Crystal or a

TTL

Signal for

Frequency Source

• Provides Local

READY

and Multibus ™

READY

Synchronization

RES--------------------------~

0

X1----I

XTAl

OSCillATOR

X2----I

F/C

----------1--1~--...._

EFI

-----------------l....J

+3

• 18·Pin Package

• Single

+5V

Power Supply

•

Generates System Reset Output from

Schmitt Trigger

Input

• Capable

of Clock Synchronization with

Other 8284As

D

RESET

OSC

PClK

RDY1

CSYNC

----------------------------...----H------'

READY

EFI

RDY1

RDY2--n-

AEN2

---(>oJ

---.-

CKt

D Q

FF1

ASYNC----------------------~

Figure 1. 8284A

Block

Diagram

64

F/C

OSC

ClK

RES

RESET

READY

Figure

2.

8284A Pin Configuration