APPENDIX

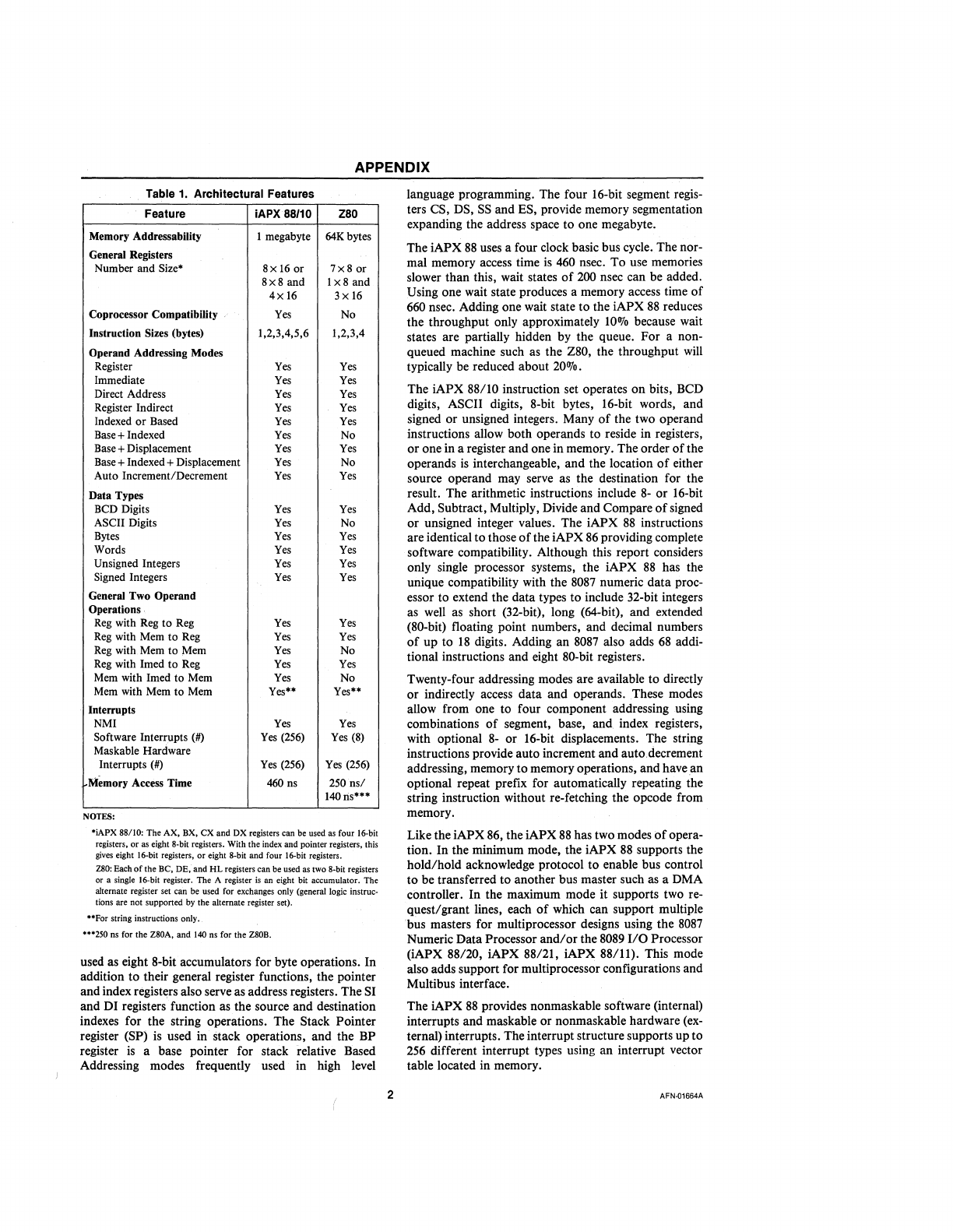

Table 1. Architectural Features

Feature

iAPX88/10

Z80

Memory

Addressability 1

megabyte

64K

bytes

General

Registers

Number

and Size·

8x

16

or

7x8

or

8x8

and

1

x8

and

4xl6

3x

16

Coprocessor Compatibility "

Yes

No

Instruction

Sizes

(bytes)

1,2,3,4,5,6 1,2,3,4

Operand Addressing

Modes

Register

Yes Yes

Immediate

Yes

Yes

Direct

Address

Yes

Yes

Register

Indirect

Yes

Yes

Indexed

or

Based

Yes

Yes

Base

+

Indexed

Yes

No

Base

+ Displacement

Yes

Yes

Base

+

Indexed

+

Displacement

Yes

No

Auto Increment/Decrement

Yes Yes

Data

Types

BCD

Digits

Yes Yes

ASCII

Digits

Yes

No

Bytes

Yes Yes

Words

Yes

Yes

Unsigned

Integers

Yes Yes

Signed

Integers

Yes Yes

General

Two

Operand

Operations,

Reg

with

Reg

to

Reg

Yes

Yes

Reg

with

Mem

to

Reg

Yes Yes

Reg

with

Mem

to

Mem

Yes

No

Reg

with

Imed

to

Reg

Yes Yes

Mem

with

Imed

to

Mem

Yes

No

Mem

with

Mem

to

Mem

Yes·· Yes··

Interrupts

NMI

Yes Yes

Software

Interrupts (#)

Yes

(256)

Yes

(8)

Maskable

Hardware

Interrupts

(#)

Yes

(256)

Yes

(256)

Memory

Access

Time

460

ns

250ns/

140 lis··*

NOTES:

*iAPX 88/10: The

AX.

BX.

ex

and

DX

registers can

be

used as

four

16-bit

registers,

or

as

eight 8-bit registers. With

the

index

and

pointer registers, this

gives eight 16-bit registers,

or

eight 8-bit

and

four 16-bit registers.

Z80: Each

of

the

BC,

DE;

and

HL

registers

can

be

used

as

two

8-bit registers

or a single 16-bit register. The A register

is

an eight bit accumulator. The

alternate register set can

be

used for exchanges only (general logic instruc-

tions are not supported by the alternate register set).

**For string instructions only

..

"·250

os for

the

Z80A,

and

140 ns for

the

ZSOB.

used as eight 8-bit accumulators for byte operations. In

addition

to

their general register functions, the pointer

and index

registc:;rs

also serve as address registers. The SI

and

01

registers function as the source

and

destination

indexes for the string operations. The Stack Pointer

register (SP) is used in stack operations,

and

the BP

register is a base pointer for stack relative Based

Addressing modes frequently used in high level

2

language programming. The four 16-bit segment regis-

ters CS, OS,

SS

and

ES, provide memory segmentation

expanding the address space

to

one megabyte.

The

iAPX

88

uses a four clock basic bus cycle. The nor-

mal memory access time is 460 nsec.

To

use memories

slower

than

this, wait states

of

200 nsec can be added.

Using one wait state produces a memory access time

of

660 nsec. Adding one wait state

to

the iAPX

88

reduces

the

throughput only approximately

10DJo

because wait

states are partially hidden by the queue.

For

a non-

queued machine such as the Z80, the throughput will

typically be reduced about

20DJo.

The

iAPX

88/10 instruction set operates

on

bits, BCD

digits, ASCII digits, 8-bit bytes, 16-bit words,

and

signed

or

unsigned integers. Many

of

the two operand

instructions allow both operands to reside in registers,

or

one in a register

and

one in memory. The order

of

the

operands is interchangeable,

and

the location

of

either

source operand may serve as the destination for the

result. The arithmetic instructions include

8-

or

16-bit

Add,

Subtract, Multiply, Divide

and

Compare

of

signed

or

unsigned integer values. The

iAPX

88

instructions

are identical

to

those

of

the

iAPX

86

providing complete

software compatibility. Although this report considers

only single processor systems, the

iAPX

88

has the

unique compatibility with the

8087 numeric

data

proc-

essor

to

extend the

data

types

to

include 32-bit integers

as well as short (32-bit), long (64-bit),

and

extended

(80-bit) floating point numbers,

and

decimal numbers

of

up

to

18

digits. Adding

an

8087 also adds

68

addi-

tional instructions and eight 80-bit registers.

Twenty-four addressing modes are available

to

directly

or

indirectly access

data

and

operands. These modes

allow from one to four component addressing using

combinations

of

segment, base, and index registers,

with optional

8-

or

16-bit displacements. The string

instructions provide auto increment

and

auto,decrement

addressing, memory

to

memory operations,

and

have.an

optional repeat prefix for automatically repeating the

string instruction without re-fetching the opcode from

memory.

Like the

iAPX

86, the iAPX

88

has two modes

of

opera-

tion.

In

the minimum mode, the

iAPX

88

supports the

hold/hold

acknowledge protocol

to

enable bus control

to

be transferred

to

another bus master such as a DMA

controller.

In

the maximum mode

it

supports two re-

quest/grant lines, each

of

which can support multiple

bus masters for multiprocessor designs using

the

8087

Numeric

Data

Processor

and/or

the 8089

I/O

Processor

(iAPX 88/20,

iAPX

88/21,

iAPX

88/11). This mode

also adds support for multiprocessor configurations and

Multibus interface.

The

iAPX

88

provides nonmaskable software (internal)

interrupts and maskable

or

nonmaskable hardware

(ex-

ternal) interrupts. The interrupt structure supports

up

to

256 different interrupt types using an interrupt vector

table located in memory.

AFN-01664A