ARCHITECTURE AND INSTRUCTIONS

Register Operands

An instruction may address

an

operand resid-

ing in one of the general registers or in one of

the pointer or index registers. Fig.

2-5

shows .

the register selection.

as

deterinined by the

"r

/

m"

field (first operand) or the "reg" field

(second operand) in the instruction.

Immediate Operands

In general, one

of

the two operands of a two-

operand instruction can be

"immediate" data

contained within

the.

instruction~

These oper-

ands are represented in 2's-complement form

and may be 8-bits or 16-bits in length.

Addressing Mode Usage

The addressing modes were designed to per-

mit efficient implementation of high-level

language features.

For

example, a simple var-

iable

is

accessed with the direct mode,

whereas

an

array element in a based record

(at a memory address pointed to by some

other base variable)

maybe

accessed within

the indirect -through-

BX

-plus-SI -plus-offset

mode

(whereBX

points to start-of-record,

offset points to the

start of the array within

the record, and index register SI contains the

..

index into the array).

The addressing modes involving the BP base

register allow accessing data· in the stack

segment instead of in the data

segment. Rec-

ursive procedures and block-structured langu-

ages frequently store data in the stack.

Address modes for accessing data elements

use effective addresses shown in Fig.

2-6.

Addressing Summary

Fig. 2-7·summarizes the address Gomponents

that are combined to generate memory

addresses. The Default segment base

is

the

segment register automatically chosen by the

;8088

for the corresponding type of memory

reference. The Alternate segment base may

replace the Default segment

if

a special "seg-

ment override" prefix precedes the instruction.

The Logical address

is automatically. added

to

the chosen segment register to form the

2-8

memory address. The

8088

Assembly lan-

guage simplifies the task of selecting the

desired addressing modes for use with basic

8088

instruction types.

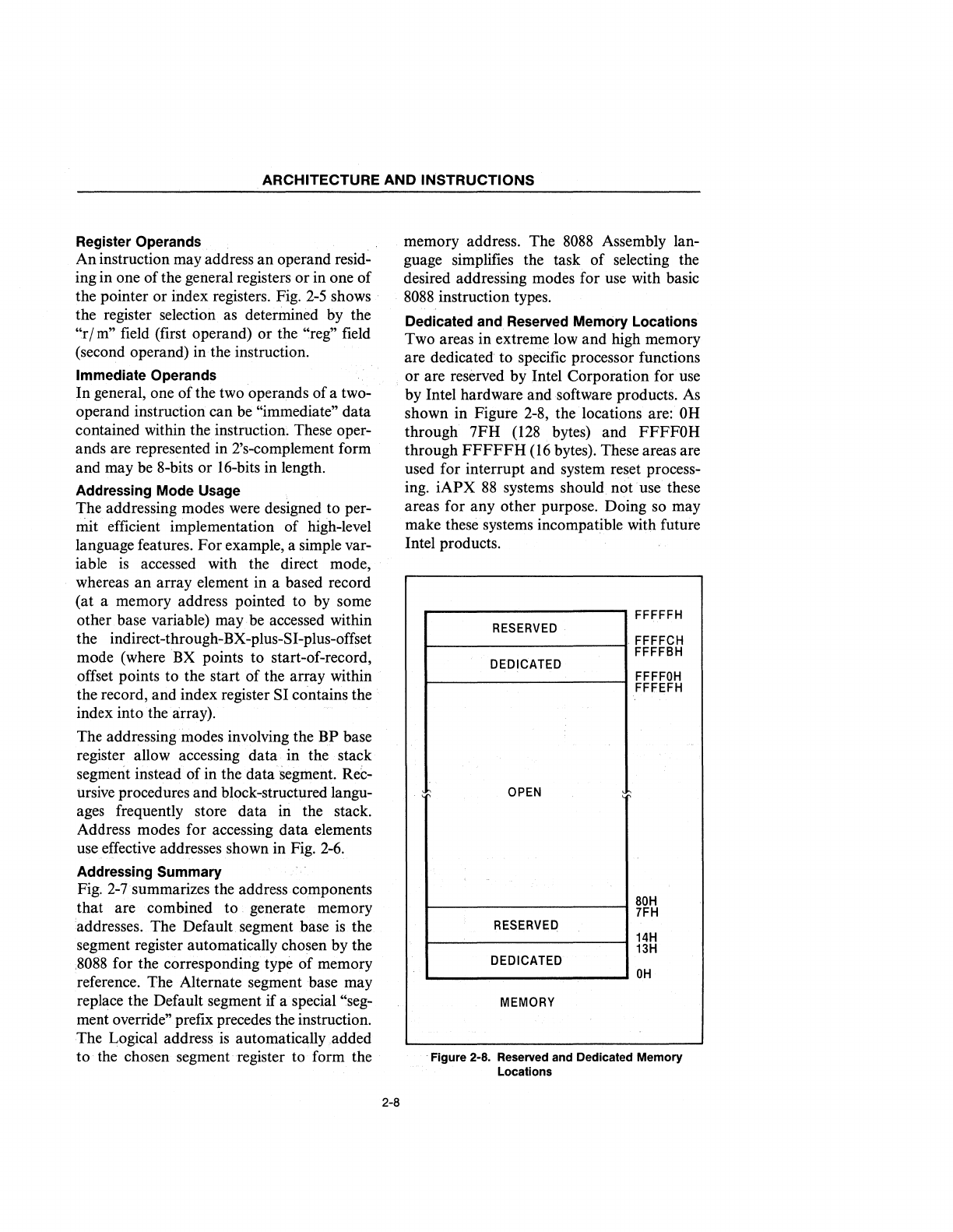

Dedicated

and

Reserved Memory Locations

Two areas in extreme low and high memory

are dedicated to specific processor functions

or are reserved by Intel Corporation for use

by Intel hardware and software products.

As

shown in Figure

2-8,

the locations are:

OH

through 7FH

(128

bytes) and FFFFOH

through

FFFFFH

(16 bytes). These areas are

used for interrupt and system reset process-

ing. iAPX

88

systems should not use these

areas for any other purpose. Doing so may

make these systems incompatible with future

Intel products.

r------------,

FFFFFH

RESERVED

r----------

.....

FFFFCH

FFFFBH

DEDICATED

r----------

.....

FFFFOH

FFFEFH

OPEN

BOH

7FH

RESERVED

14H

13H

DEDICATED

OH

MEMORY

. Figure 2-8. Reserved and Dedicated Memory

Locations