HARDWARE DESIGN

The hysteresis specified in the 8284A data

sheet implies that at least

0.25 volts will

separate the logic

0 and I switching point of

the 8284A reset input. Inputs without hys-

teresis switch from

LOW to

HIGH

and

HIGH to LOW at approximately the same

voltage threshold. The inputs are guaranteed

SIGNAL

:

CONDITION

ADO-AD?

*

FLOAT

A8-A15

SSO

*

101M

*

DT/R

*

DEN

DRIVEN HIGH,

*

THEN FLOAT

WR

*

RD

*

INTA

ALE

*

LOW

HLDA

Figure 3-15. iAPX

88

Bus Condition During Reset

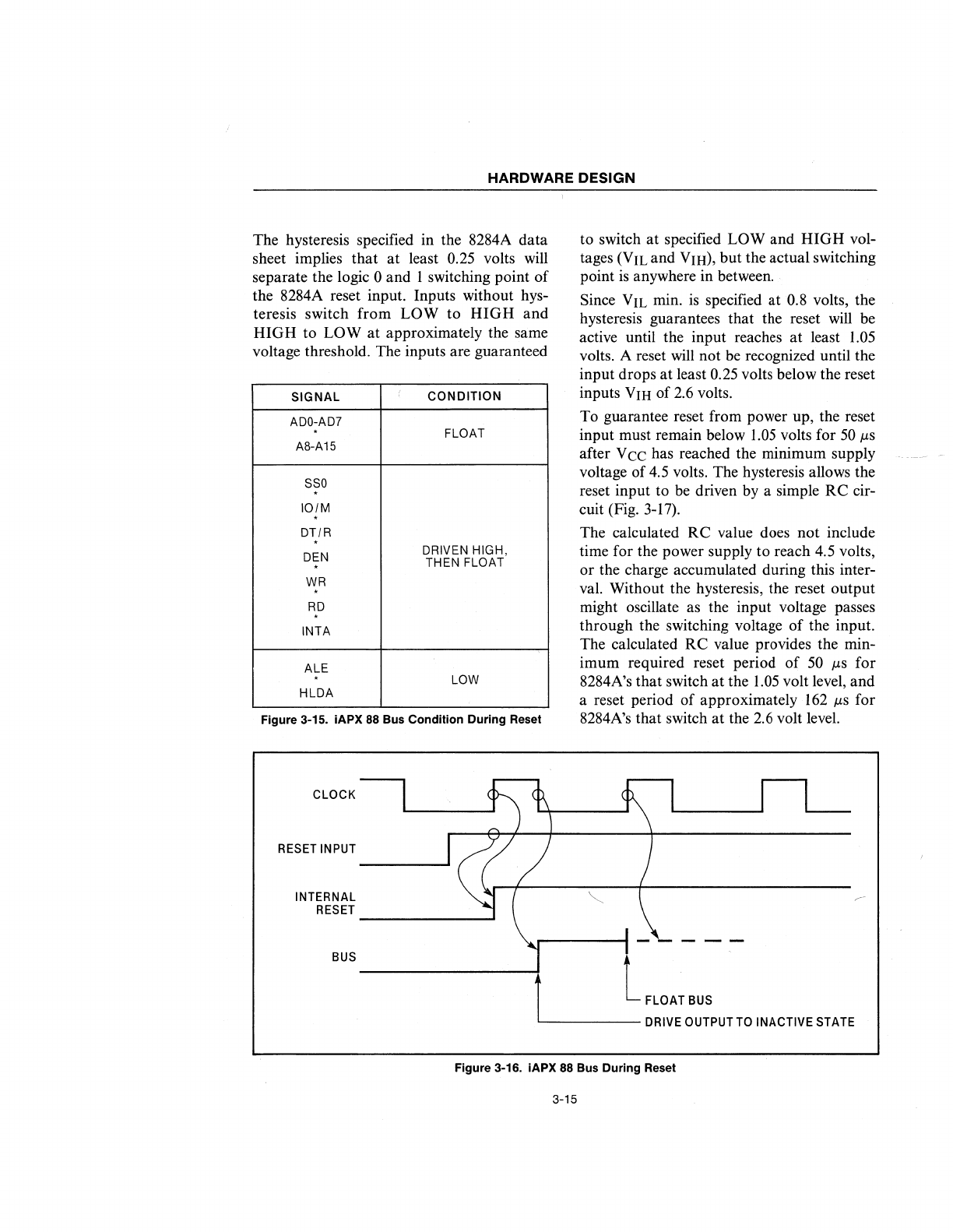

CLOCK

RESET INPUT

iNTERNAL

RESET

_______

...1

to switch at specified LOW and HIGH vol-

tages

(VIL and VIH), but the actual switching

point

is

anywhere in between.

Since

VIL min.

is

specified at 0.8 volts, the

hysteresis guarantees that the reset

will

be

active until the input reaches

at

least

1.05

volts. A reset

will

not be recognized until the

input drops

at

least 0.25 volts below the reset

inputs

VIH of 2.6 volts.

To guarantee reset from power up, the reset

input must remain below

1.05

volts for

50

p,s

after Vee has reached the minimum supply

voltage of 4.5 volts. The hysteresis allows the

reset input to

be

driven by a simple

RC

cir-

cuit (Fig.

3-17).

The calculated

RC

value does

not

include

time for the power supply to reach 4.5 volts,

or the charge accumulated during this inter-

val. Without the hysteresis, the reset output

might oscillate as the input voltage passes

through the switching voltage

of

the input.

The calculated

RC

value provides the min-

imum required reset period

of

50

p,s

for

8284A's that switch

at

the

1.05

volt level, and

a reset period of approximately

162

p,s

for

8284A's that switch

at

the

2.6

volt level.

r------I

- - - - -

BUS

FLOAT BUS

L-

_____

DRIVE OUTPUT TO INACTIVE STATE

Figure 3-16. iAPX

88

Bus During Reset

3-15