INTRODUCTION

Bus Interface and Execution Units

Work in

Parallel

The 8088 has a separate bus interface unit

called the

BIU whose only job

is

to fetch

instructions from memory and pass data to

and from the execution hardware to the out-

side world over the bus interface. Since the

execution unit and the bus interface unit are

independent, the bus interface unit fetches

additional instructions while the execution

unit (sometimes called the

EU) executes a

previous instruction. This

is

made possible

by the instruction pipeline (or queue)

between the bus interface unit and the execu-

tion unit; the bus interface unit fills this

pipeline with instructions awaiting execu-

tion. Thus, whenever the execution unit

finishes executing a given instruction, the

next instruction

is

usually ready for imme-

diate execution without delays caused by

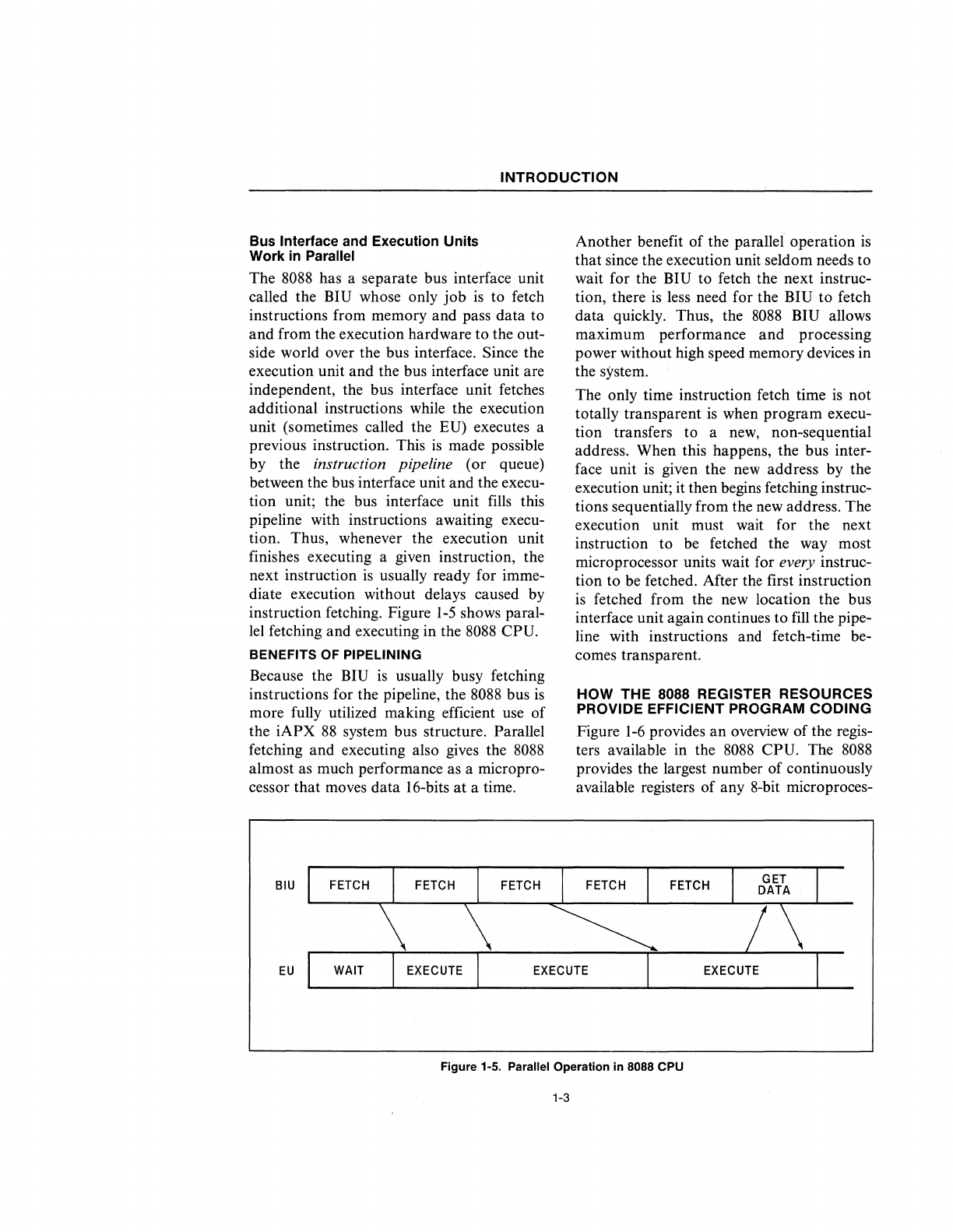

instruction fetching. Figure

1-5

shows paral-

lel

fetching and executing in the

8088

CPU.

BENEFITS

OF

PIPELINING

Because the BIU

is

usually busy fetching

instructions for the pipeline, the

8088

bus

is

more fully utilized making efficient use of

the iAPX

88

system bus structure. Parallel

fetching and executing also gives the

8088

almost as much performance as a micropro-

cessor that moves data 16-bits

at

a time.

BIU

Another benefit of the parallel' operation

is

that since the execution unit seldom needs to

wait for the

BIU to fetch the next instruc-

tion, there

is

less need for the BIU to fetch

data quickly. Thus, the

8088

BIU allows

maximum performance

and

processing

power without high speed memory devices in

the system.

The only time instruction fetch time

is

not

totally transparent

is

when program execu-

tion transfers to a new, non..:sequential

address. When this happens, the bus inter-

face unit

is

given the new address by the

execution unit; it then begins fetching instruc-

tions sequentially from the new address. The

execution unit must wait for the next

instruction to be fetched the way most

microprocessor units wait for every instruc-

tion to be fetched. After the first instruction

is

fetched from the new location the bus

interface unit again continues to fill the pipe-

line with instructions and fetch-time be-

comes transparent.

HOW THE 8088 REGISTER RESOURCES

PROVIDE EFFICIENT PROGRAM

CODING

Figure

1-6

provides

an

overview of the regis-

ters available in the

8088

CPU. The

8088

provides the largest number of continuously

available registers of any 8-bit microproces-

EU

WAIT

EXECUTE

EXECUTE EXECUTE

Figure 1-5. Parallel Operation

in

8088 CPU

1-3