APPENDIX

10. Interrupt Response

This program accepts an interrupt, pushes all the

proc-

essor registers (except the Stack Pointer) on

to

the stack,

and jumps to a service routine.

All

registers are restored

before returning from the service routine. This program

also considers the worst case latency due to finishing the

longest instruction. This

is

because when an interrupt

occurs

it

must wait to be processed until after the com-

pletion

of

the current instruction. The times are mea-

sured both with and without this latency. (For each

application where interrupt response

is

critical, the

designer should only consider the longest instruction his

system

will

use.)

RESULTS

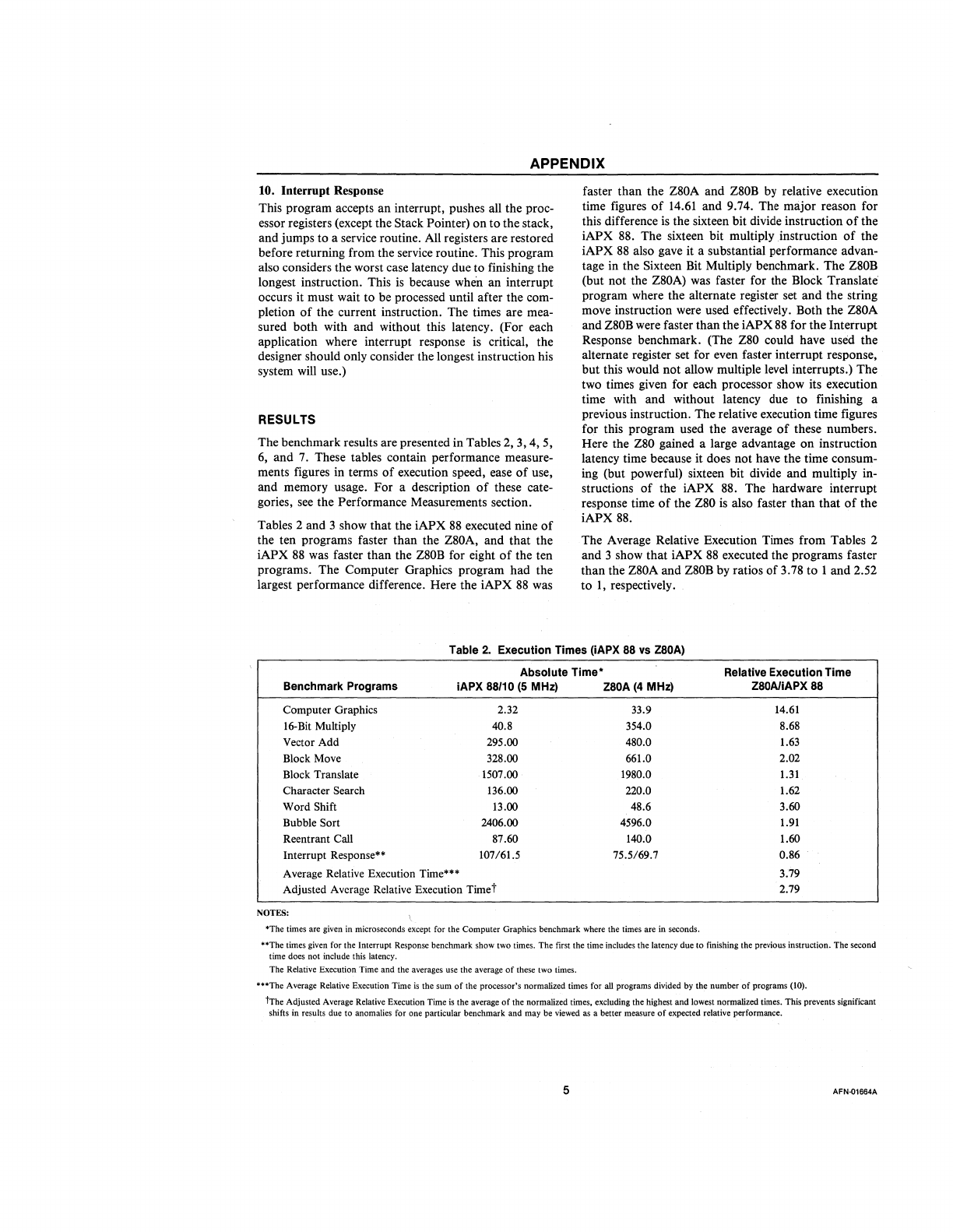

The benchmark results are presented in Tables 2, 3,

4,5,

6,

and

7.

These tables contain performance measure-

ments figures in terms

of

execution speed, ease

of

use,

and memory usage. For a description

of

these cate-

gories,

see

the Performance Measurements section.

Tables 2 and 3 show that the

iAPX

88

executed nine

of

the ten programs faster than the Z80A, and that the

iAPX

88

was

faster than the

Z80B

for eight

of

the ten

programs. The Computer Graphics program had the

largest performance difference. Here the iAPX

88

was

faster than the

Z80A and

Z80B

by

relative execution

time figures

of

14.61

and 9.74. The major reason for

this difference

is

the sixteen bit divide instruction

of

the

iAPX

88.

The sixteen bit multiply instruction

of

the

iAPX

88

also gave it a substantial performance advan-

tage in the Sixteen Bit Multiply benchmark. The Z80B

(but not the Z80A) was faster for the Block Translate'

program where the alternate register set and the string

move instruction were used effectively. Both the

Z80A

and

Z80B

were faster than the iAPX

88

for the Interrupt

Response benchmark. (The

Z80 could have used the

alternate register set for even faster interrupt response,

but this would not allow multiple

level

interrupts.) The

two times given for each processor show its execution

time with and without latency due

to

finishing a

previous instruction. The relative execution time figures

for this program used the average

of

these numbers.

Here the

Z80

gained a large advantage on instruction

latency time because it does not have the time

consum-

ing (but powerful) sixteen bit divide and multiply in-

structions

of

the iAPX

88.

The hardware interrupt

response time

of

the Z80

is

also faster than that

of

the

iAPX

88.

The Average Relative Execution Times from Tables 2

and 3 show that iAPX

88

executed the programs faster

than the

Z80A and Z80B by ratios of 3.78

to

1 and 2.52

to

1,

respectively.

Table

2.

Execution Times (iAPX 88

vs

ZSOA)

Absolute Time"

Benchmark Programs iAPX

88110

(5

MHz)

ZSOA

(4

MHz)

Computer

Graphics

16-Bit Multiply

Vector

Add

Block Move

Block Translate

Character Search

Word

Shift

Bubble

Sort

Reentrant Call

Interrupt Response"

2.32

40.8

295.00

328.00

1507.00

136.00

13.00

2406.00

87.60

107/61.5

Average Relative Execution

Time'·'

Adjusted Average Relative Execution

Timet

NOTES:

33.9

354.0

480.0

661.0

1980.0

220.0

48.6

4596.0

140.0

75.5/69.7

*The

times

are

given

in

microseconds

except

for

the

Computer

Graphics

benchmark

where

the

times

are

in

seconds.

Relative Execution Time

Z80AlIAPX 88

14.61

8.68

1.63

2.02

1.31

1.62

3.60

1.91

1.60

0.86

3.79

2.79

··The

times

given

for

the

Interrupt

Response

benchmark

show

two

times.

The

first

the

time

includes

the latency

due

to finishing

the

previous

instruction.

The

second

time does not include this latency.

The Relative Execution Time and the averages use the average

of

these two times.

··*The

Average

Relative

Execution

Time

is

the

sum

of

the

processor's

normalized

times

for

all

programs

divided

by

the

number

of

programs

(10).

trhe

Adjusted

Average

Relative

Execution

Time

is

the

average

of

the

normalized

times.

excluding

the

highest

and

lowest normalized

times.

This

prevents

significant

shifts

in

results

due

to

anomalies

for

one

particular

benchmark

and

may

be

viewed

as

a

better

measure

of

expected

relative

performance.

5 AFN·01664A