HARDWARE DESIGN

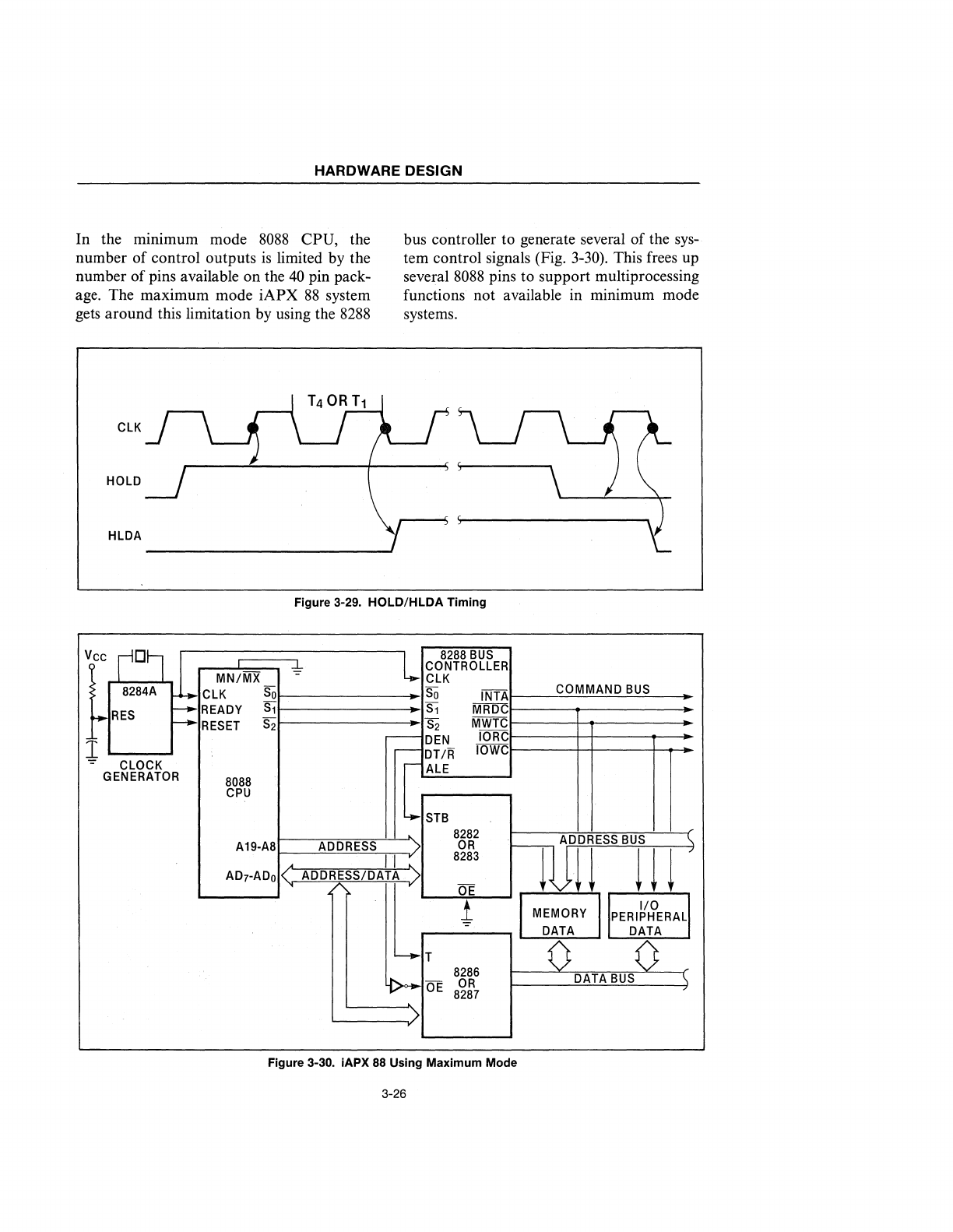

In the minimum mode

8088

CPU, the

number of control outputs

is

limited by the

number of pins available on the

40

pin pack-

age. The maximum mode

iAPX

88

system

gets around this limitation by using the

8288

ClK

HOLD

HlDA

bus controller to generate several of the

sys-

tem control signals (Fig.

3-30).

This frees up

several

8088

pins to support multiprocessing

functions not available in minimum mode

systems.

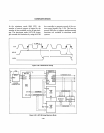

Figure 3-29.

HOlD/HlDA

Timing

Vce

r

D

1

L

8288

BUS

-=l=-

CONTROllER

MN/MX

ClK

8284A

....

ClK

So

So

INTA

COMMAND

BUS

[-

READY

S1

S1

MRDC

~

RES

[-

RESET

S2

S2

MWTC

r---

DEN

10RC

J

~

DT/R"

10WC

CLOCK

r-

ALE

GENERATOR

8088

CPU

~

STB

8282

lliDRESSBU[

1

\

A19-A8 ADDRESS

>

OR

.-

II

8283

ADrADol<

ADDRESS/DATA )

•

L,

OE

i

MEMORY

1/0

PERIPHERAL

DATA DATA

0 0

8286

~

OE

OR

DATA BUS

\

8287

-'

>

Figure 3-30. iAPX 88 Using

Maximum

Mode

3-26