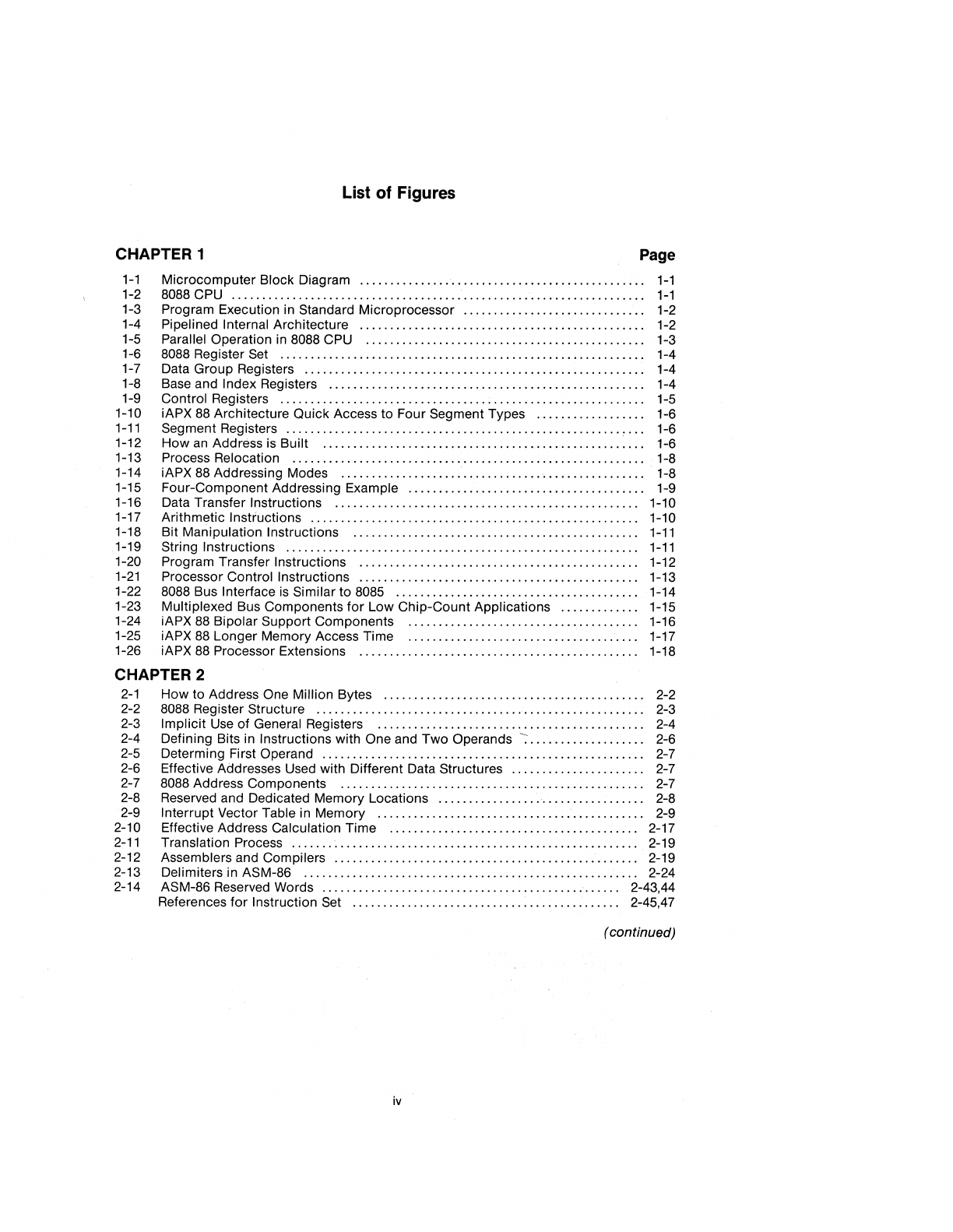

List of Figures

CHAPTER

1

Page

1-1

Microcomputer Block Diagram

...............................................

1-1

1-2 8088 CPU

....................................................................

1-1

1-3 Program Execution in Standard Microprocessor

..............................

1-2

1-4

Pipelined Internal Architecture

...............................................

1-2

1-5

Parallel Operation in 8088 CPU

..............................................

1-3

1-6

8088

Register Set

............................................................

1-4

1-7 Data Group Registers

........................................................

1-4

1-8 Base and

Index Registers

....................................................

1-4

1-9

Control Registers

............................................................

1-5

1-10 iAPX

88

Architecture Quick Access to Four Segment Types

..................

1-6

1-11

Segment Registers

.......................................................

,'

...

1-6

1-12 How

an

Address is Built

.....................................................

1-6

1-13 Process

Relocation

..........................................................

1-8

1-14 iAPX

88

Addressing Modes

..................................................

1-8

1-15 Four-Component Addressing

Example

.......................................

1-9

1-16 Data Transfer

Instructions

..................................................

1-10

1-17 Arithmetic

Instructions

......................................................

1-10

1-18 Bit

Manipulation Instructions

...............................................

1-11

1-19 String Instructions

..........................................................

1-11

1-20 Program Transfer Instructions

..............................................

1-12

1-21

Processor Control Instructions

..............................................

1-13

1-22 8088 Bus

Interface is Similar to

8085

........................................

1-14

1-23

Multiplexed Bus Components for Low Chip-Count Applications

.............

1-15

1-24 iAPX

88

Bipolar Support Components

......................................

1-16

1-25 iAPX

88

Longer Memory Access Time

......................................

1-17

1-26 iAPX

88

Processor Extensions

..............................................

1-18

CHAPTER

2

2-1

How to Address One Million Bytes

...........................................

2-2

2-2 8088 Register Structure

......................................................

2-3

2-3

Implicit Use of General Registers

............................................

2-4

2-4 Defining Bits in

Instructions with One and Two Operands

-:...................

2~6

2-5 Determing First Operand

.....................................................

2-7

2-6 Effective Addresses Used with Different Data Structures

......................

2-7

2-7 8088 Address Components

..................................................

2-7

2-8 Reserved and Dedicated Memory Locations

..................................

2-8

2-9

Interrupt Vector Table in Memory

............................................

2-9

2-10 Effective Address Calculation Time

.........................................

2-17

2-11

Translation Process

.........................................................

2-19

2-12

Assemblers and Compilers

..................................................

2-19

2-13

Delimiters in ASM-86

.......................................................

2-24

2-14 ASM-86 Reserved Words

.................................................

2-43,44

References for

Instruction Set

............................................

2-45,47

(continued)

iv