iAPX 88/10

Bus

Operation

.

The

8088 address/data bus is broken into three parts -

the lower eight address/data bits (ADO-AD?), the middle

eight address bits (A8-A15), and the upper four address

bits (A16-A19). The address/data bits and the highest

four address

bits

are time multiplexed. This technique

provides the

most·

efficient use

of

pins on the proc-

essor, permitting the use

of

a standard

40

lead package.

The middle eight address bits are not multiplexed, i.e.

they remain valid throughout each bus cycle.

In addi-

tion, the bus can

be

demultiplexed at the processor with

a single address latch

if

a standard, non-multiplexed

bus is desired for the system.

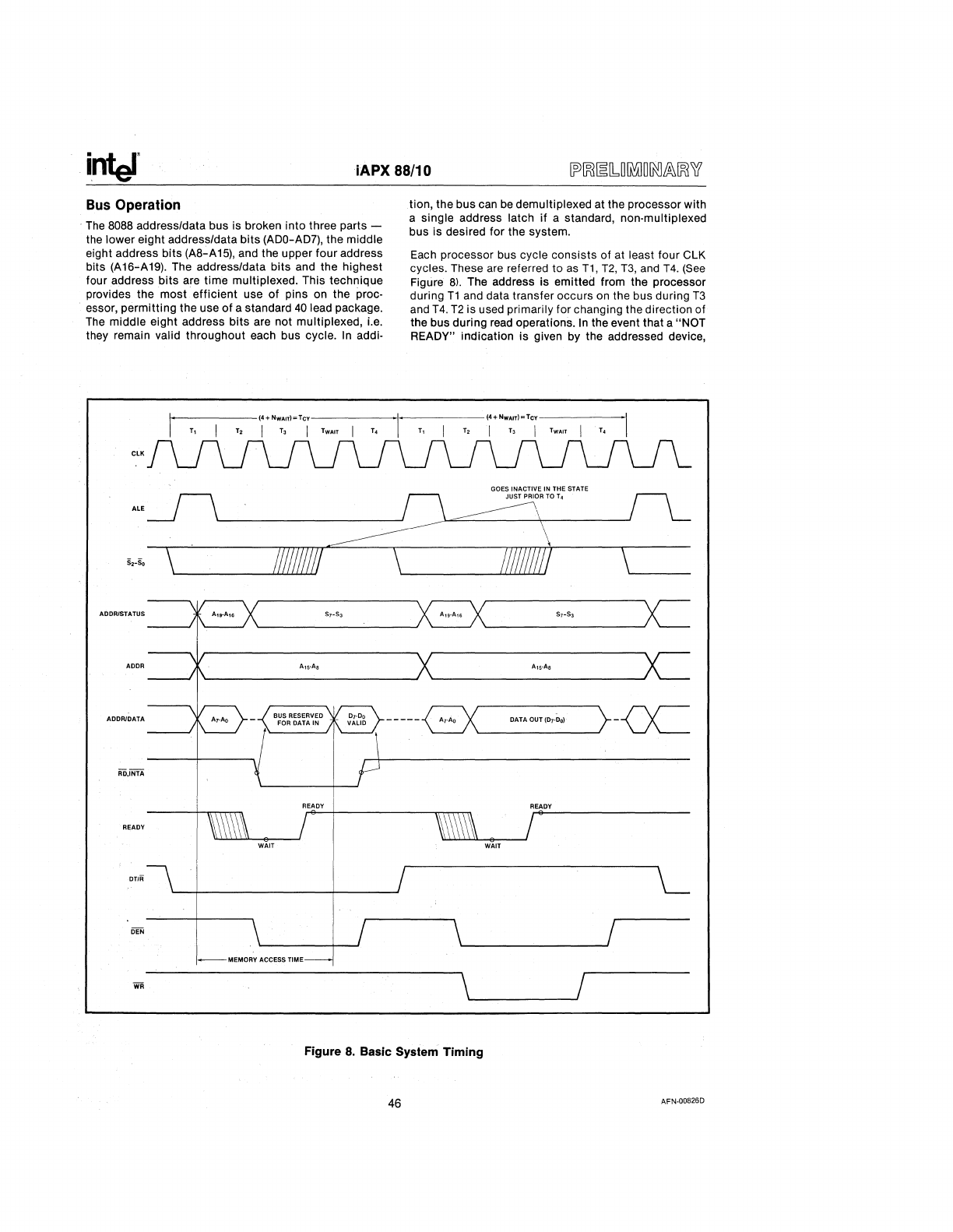

Each processor bus cycle consists of at least four

elK

cycles. These are referred

to

as

T1,

T2,

T3,

and

T4.

(See

Figure

8>'

The address is emitted from the processor

during

T1

and data transfer occurs

on

the bus during

T3

and

T4.

T2

is used primarily for changing the direction of

the bus during read operations.

In the event that a "NOT

READY" indication is given by the addressed device,

!-------(4+NWAIT)=Tcv------------(4+NwAITl=TCy--------1

T,

T, T,

T,

TWAIT I . T4

elK

GOES INACTIVE IN

THE

STATE

U/UP&=1?

~'.

\'----

ADDRISTATUS

AODR

ADDRIDATA

-----G'-

__

D_AT_A_O_uT_ID_r_DoJ

___

>--~

READY

DT/R

\~-_/

Figure

8.

Basic System Timing

46

AFN.Q0826D