intJ

8284A

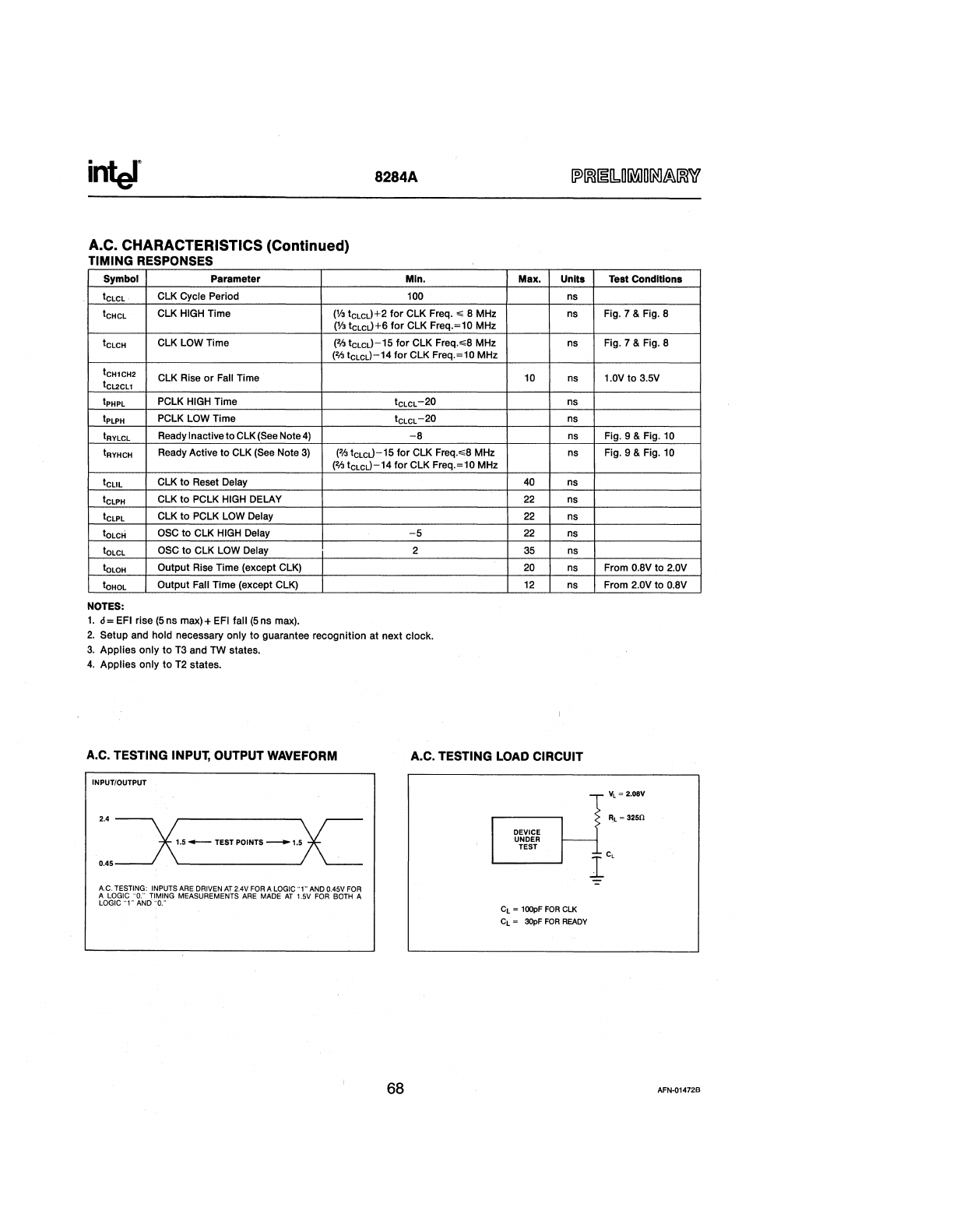

A.C. CHARACTERISTICS (Continued)

TIMING

RESPONSES

Symbol Parameter Min.

tCLCL

CLK Cycle Period 100

tCHCL

CLK

HIGH

Time

('13

tCLcd+2

for

CLK Freq.

,,;;

8

MHz

(Y3

tCLcd+6

for

CLK Freq.=10 MHz

tCLCH

CLK LOW Time

(% tCLcd-15

for

CLK

Freq.,,;;8

MHz

(% tCLcL)-14 for CLK Freq.=10 MHz

tCH1CH2

CLK Rise

or

Fall Time

tCL2CLl

tpHPL

PCLK

HIGH

Time

tCLCL-20

t

pLPH

PCLK LOW Time

tCLCL

-20

tRYLCL

Ready Inactive

to

CLK

(See

Note

4)

-8

tRYHCH

Ready Active

to

CLK

(See

Note

3)

(%

tCLcd-15 for CLK

Freq.,,;;8

MHz

(%

tCLcd-14

for

CLK Freq.=10 MHz

tCLIL

CLK

to

Reset Delay

t

CLPH

CLK to PCLK

HIGH

DELAY

tCLPL

CLK

to

PCLK LOW Delay

tOLCH

OSC

to

CLK

HIGH

Delay

-5

tOLCL

OSC

to

CLK LOW Delay

2

tOLOH

Output Rise Time (except

CLK)

IoHoL

Output Fall Time (except eLK)

NOTES:

1.

,,=

EFI

rise

(5

ns max) +

EFI

fall

(5

ns max).

2.

Setup and hold necessary only

to

guarantee recognition at next clock.

3.

Applies only

to

T3

and

TW

states.

4.

Applies only

to

T2

states.

Max. Units Test Conditions

ns

ns

Fig.

7 & Fig. 8

ns Fig.

7 & Fig. 8

10 ns 1.0V

to

3.5V

ns

ns

ns

Fig. 9 & Fig.

10

ns Fig. 9 & Fig.

10

40 ns

22

ns

22

ns

22

ns

35

ns

20

ns

From

O.BV

to

2.OV

12

ns From

2.OV

to

0.8V

A.C. TESTING INPUT, OUTPUT WAVEFORM

A.C. TESTING LOAD CIRCUIT

INPUT/OUTPUT

A.C.

TESTING:

INPUTS

ARE

DRIVEN

AT

2.4V

FORA

LOGIC

"I"

AND

0.45V

FOR

A

LOGIC

"D."

TIMING

MEASUREMENTS

ARE

MADE

AT

1.5V

FOR

BOTH

A

LOGIC

"I"

AND

"D."

68

"'T'"

VL: '.oav

RJ.

= 32sn

DEVICE

UNDER

I--

TEST

r

CL

CL

:

l00pF

FOR

CLK

CL:

30pF

FOR

READY

AFN'()1472B