INTRODUCTION

Well-Planned Instructions

The

8088

instructions can be from one byte

to seven bytes in length, depending on the

number of operands and immediate data

fields included in the instruction. Great care

has been taken in the design of the instruc-

tion set to allow for efficient programs to be

written. The

8088

instructions need not

be

word aligned (starting

at

even addresses) con-

trary to many other 16-bit instruction sets,

therefore saving bytes otherwise wasted.

It

is

also possible to use one-byte constants, one-

byte displacements, and

jump

offsets, saving

code when compared with other machines

that always require 16-bit quantities

be

used.

The

8088

instruction set also has been

designed such that some registers are always

used for certain functions. The CX register,

for example, is used for a count value by

some repetitive instructions. This implied use

of registers allows shorter programs because

the register address need not be contained in

those instructions.

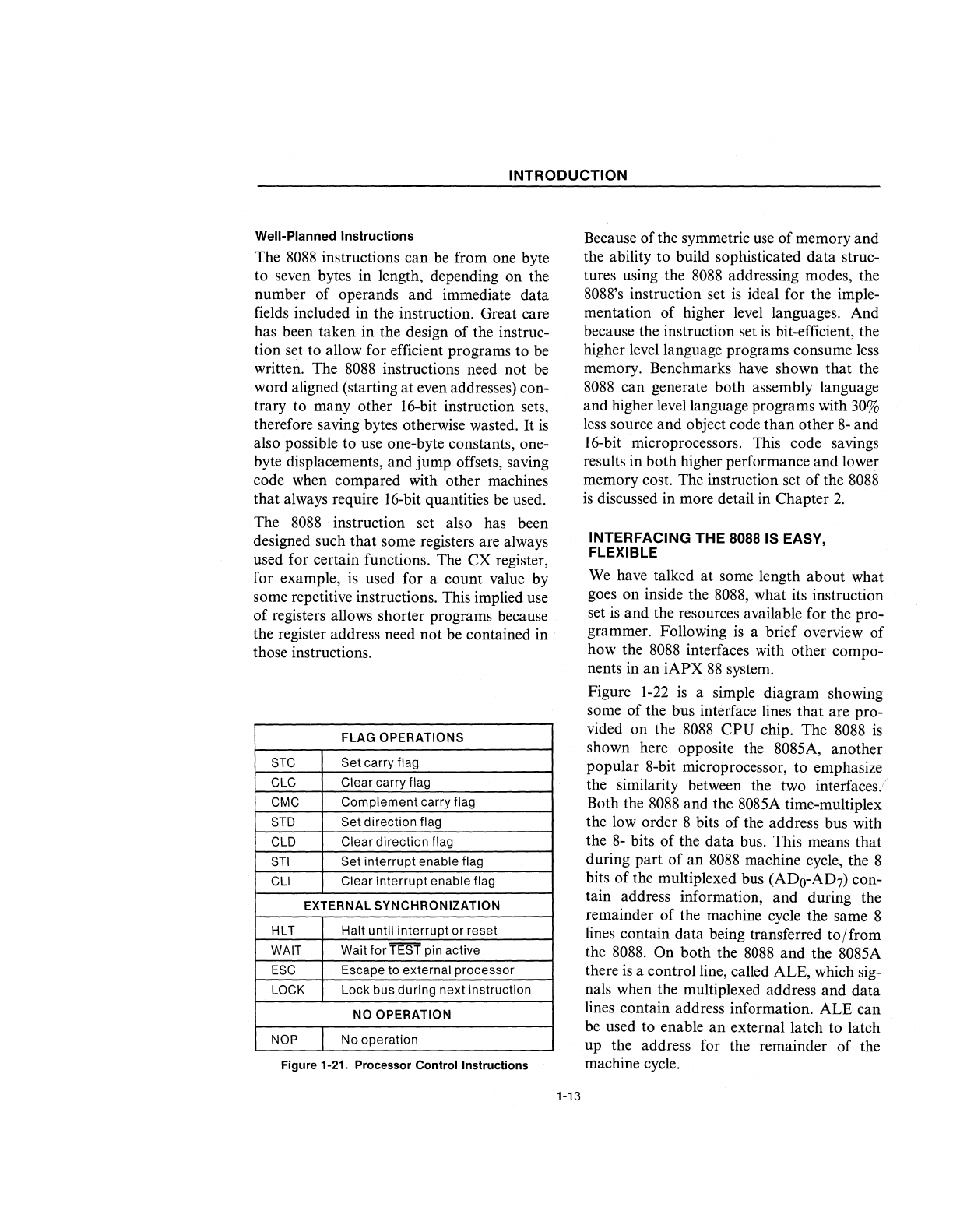

FLAG OPERATIONS

STC

Set carry flag

CLC

Clear carry flag

CMC

Complement

carry flag

STD

Set direction flag

CLD

Clear direction flag

STI

Set

interrupt

enable flag

CLI

Clear

interrupt

enable flag

EXTERNAL SYNCHRONIZATION

HLT

Halt until interrupt or reset

WAIT

Wait for TEST pin active

ESC

Escape to external processor

LOCK

Lock bus during

next

instruction

NO

OPERATION

NOP

No operation

Figure 1-21. Processor Control Instructions

1-13

Because of the symmetric use of memory and

the ability to build sophisticated

data

struc-

tures using the

8088

addressing modes, the

8088's instruction set

is

ideal for the imple-

mentation of higher level languages. And

because the instruction set

is

bit-efficient, the

higher level language programs consume less

memory. Benchmarks have shown that the

8088

can generate

both

assembly language

and higher level language programs with

30%

less source and object code

than

other

8-

and

l6-bit microprocessors. This code savings

results in both higher performance and lower

memory cost. The instruction set of the

8088

is

discussed in more detail in Chapter

2.

INTERFACING THE 8088 IS EASY,

FLEXIBLE

We

have talked

at

some length about what

goes on inside the 8088, what its instruction

set

is

and the resources available for the pro-

grammer. Following

is

a brief overview of

how the

8088

interfaces with other compo-

nents in

an

iAPX

88

system.

Figure

1-22

is

a simple diagram showing

some of the bus interface lines that are pro-

vided on the

8088

CPU

chip. The 8088

is

shown here opposite the 808SA, another

popular 8-bit microprocessor, to emphasize

the similarity between the two interfaces.

Both the

8088

and the 808SA time-multiplex

the low order 8 bits of the address bus with

the

8-

bits

of

the

data

bus. This means that

during part of an

8088

machine cycle, the 8

bits

of

the multiplexed bus (ADo-AD7) con-

tain address information,

and

during the

remainder of the machine cycle the same 8

lines contain data being transferred to

I from

the

8088.

On both the

8088

and the 808SA

there

is

a control line, called ALE, which sig-

nals when the multiplexed address and

data

lines contain address information.

ALE

can

be used to enable

an

external latch to latch

up the address for the remainder of the

machine cycle.