intJ

iAPX 88/10

elK

'MNIIIX~Vc:c

r

READY

I~'MM~--------------------------------------------------------------------------~

D

8284A

RES~

~~--------------------------------~r-------------~----------1-------~----~

n.~------------------------~4---------~~~------~-----+~~

....

CPUrnn,~

________________________

~

______

~~

__________

-i-+

__

~

______

4-

______

-+-+

__

~

r---:l

DTIII

r------,

DEIIt----l1

ALE

~STB

GNDII7

OE

8282

ADo-AD,

LATCH

At-AllrCOR/DAr

(1,20R3)

I

I

I

ADDRESS

INTA

MNfM)! OND

D=~

F

L~~'~~~I~TA

1~1

~1:;:::=1~r

~1~1

~

,J.ll

I 2142

RAM

(2,WE

""'1

I

"16'2PROMill!!IICS

MCS.:"'"

I

PERIPHERAL

1251A

V

I~~~~~~~

f--

INT

Vt--I

L....--1~IRO-7

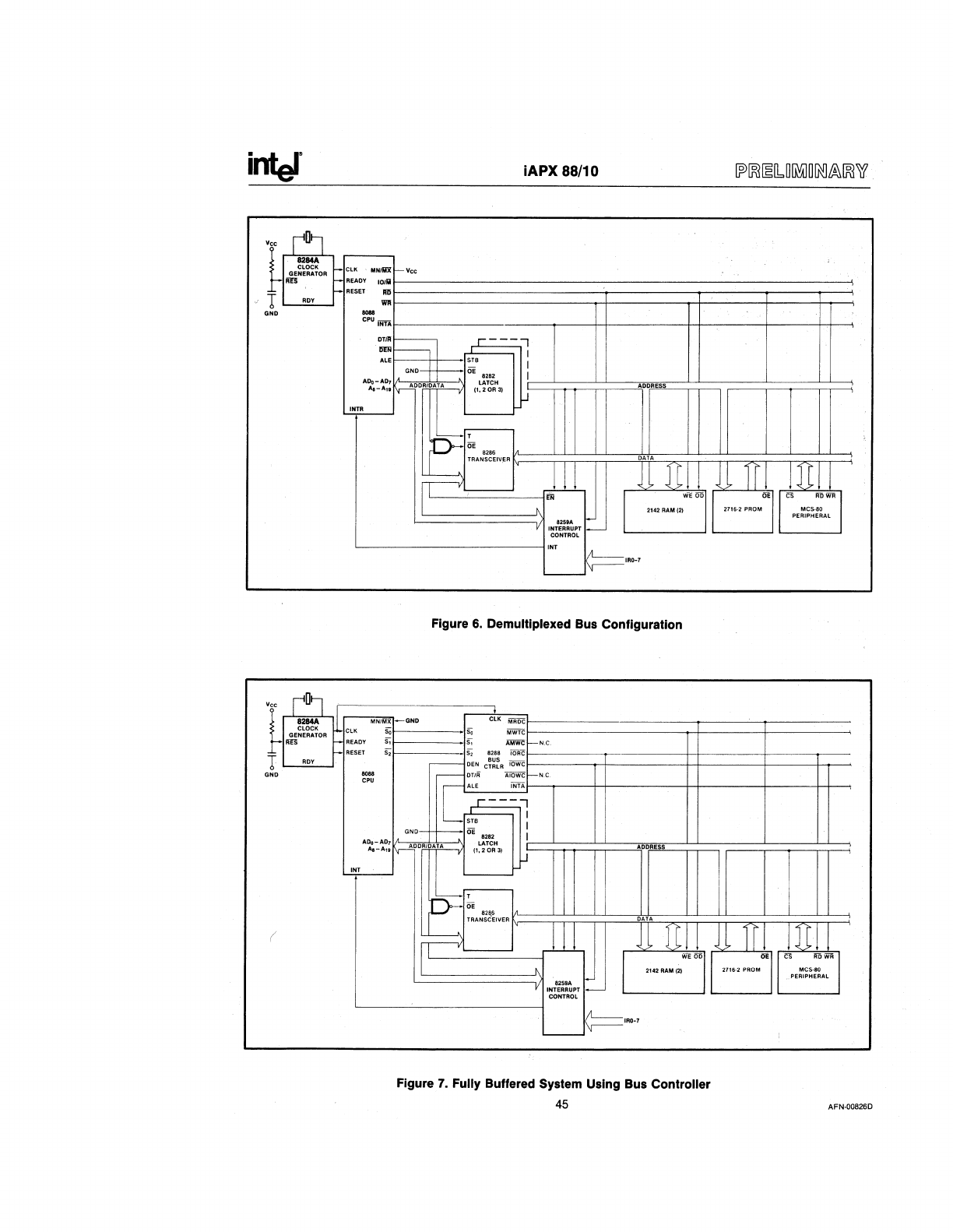

Figure

6.

Demultiplexed Bus Configuration

j

ClK

MRDe

11"l

d

CLOCK

S,

So

MWTC

GENERATOR

elK

So

m READY

RESET

S,

I

ROY

GNO

8088

CPU

ADo-AD,

"a-An

'NT

(

So

AMWC

I--N.C.

S,

8288 IORC

~

DEN

C~~~R

lowe

r---

DT/R

Alowe

I--N.C

ALE

INTA

r---:l

I

ST.

I

GNO-

I---

OE

8282

I

~DORIDA~

LATCH

ADDRESS

(1,2DR31

W

p::

T

0-

821\,6

DA

A

TRANSCEIVER

F

ill

1

11

1

11

n

I

WE

""I

I ill! 1 I

~

~"'"

I

~

2142 RAM (2) 2718·2 PROM . MC5-ao

I-

. PERIPHERAL

V

....

A

INTERRUPT

1-

CONTROL

'----

!<i=='RO-'

Figure

7.

Fully Buffered System Using Bus Controller

45

AFN.()OB2lID