SHR

SHIFT

LOGICAL

RIGHT

SHR

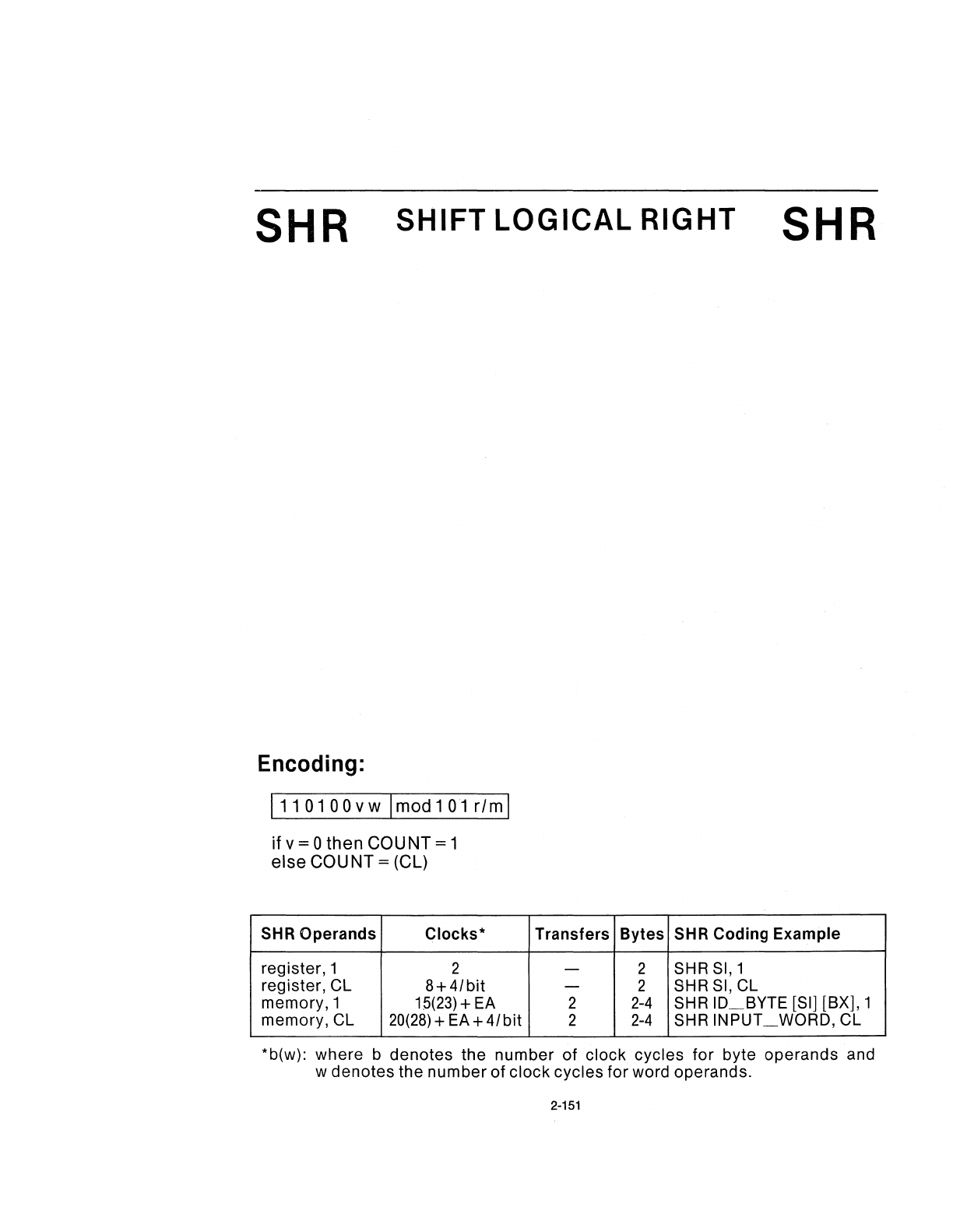

Encoding:

111

01

00

v w 1 mod 1 01 rIm 1

if

v = 0

then

COUNT = 1

else

COUNT = (CL)

SHR Operands

Clocks·

register, 1 2

register, CL

8+

4/bit

memory, 1

1.5(23)

+

EA

memory, CL

20(28)

+

EA

+

41

bit

Transfers Bytes

SHR Coding Example

-

2 8HR

81,1

-

2

SHR

81,

CL

2

2-4

8HR

ID_BYTE

[81]

[BX], 1

2

2-4

8HR

INPUT_WORD,

CL

*b(w): where b

denotes

the number

of

clock cycles

for

byte operands and

w

denotes

the

number

of clock cycles for word operands.

2-151