INTRODUCTION

addressability and 64,000 bytes of

IIO

addressability.

The iAPX

88

instruction set includes a full

complement of arithmetic operations includ-

ing addition, subtraction, multiplication, and

division, on 8-bit or 16-bit quantities. This

gives the

8088

the highest computational

throughput of any 8-bit microprocessor for

numerics intensive applications. The

8088

also has a complete set of string manipula-

tion operations for performance and flexi-

bility

in

applications where large amounts of

data are involved.

To make efficient use of its megabyte of

memory addressing, the

8088

provides the

most powerful range of addressing modes

available to the programmer; from simple

immediate addressing (data contained in the

instruction) to complex addressing built from

four components (three registers plus imme-

diate data). More details are provided on

addressing modes later on in this chapter.

The

8088

has built-in hardware support for

multi-processor systems to coordinate re-

source sharing of memory or peripheral

devices among multiple processors.

Finally, and possibly the most powerful

advantage: the

8088

is

100%

code compatible

with the 16-bit

8086 CPU.

All

the power of

the

8086

16-bit instruction set

is

available in

the 8-bit

8088.

So, iAPX

88

systems ani easily

upgradable to iAPX

86

16-bit systems because

of this complete instruction set compatibility.

FETCH

EXECUTE

TIME -

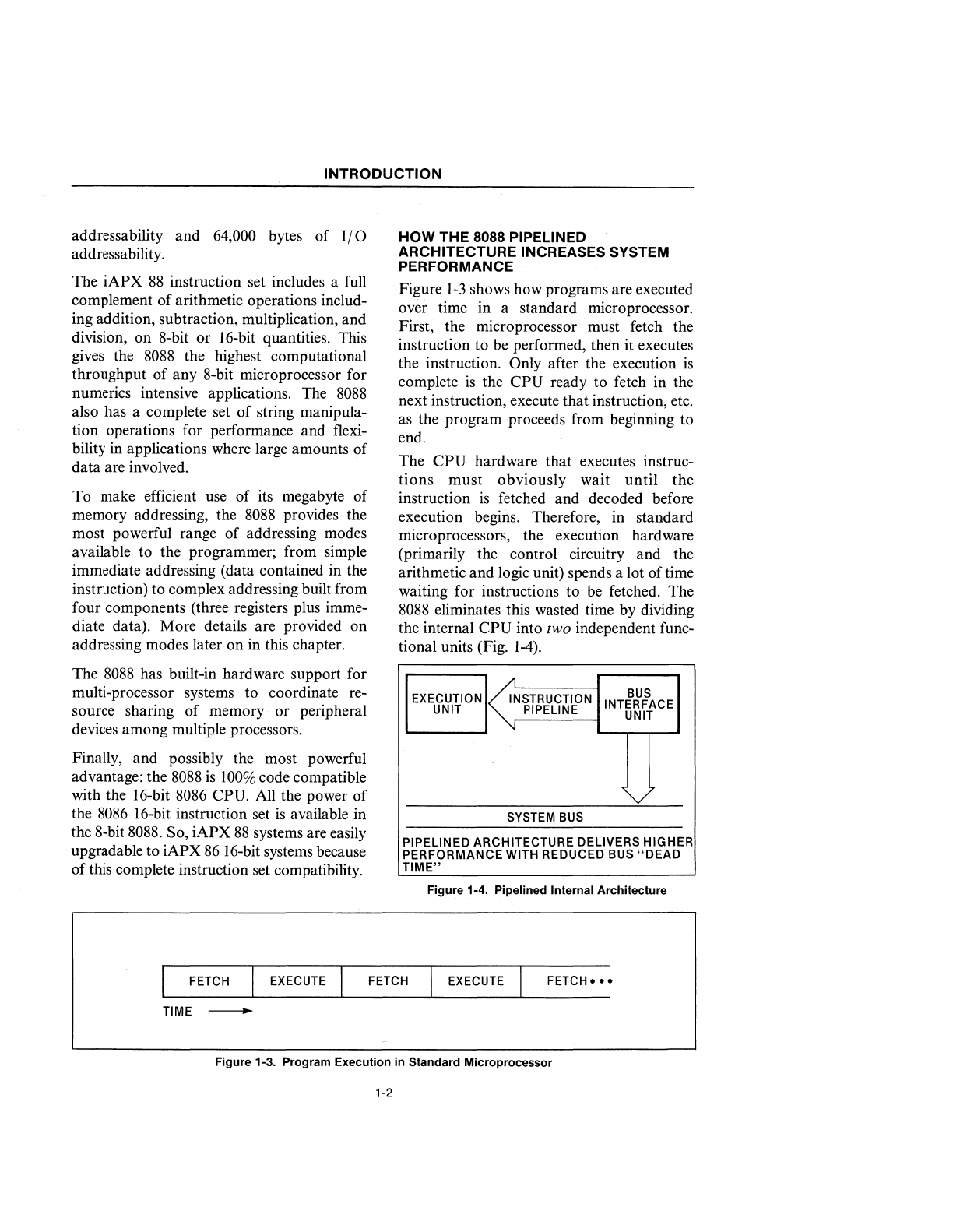

HOW

THE 8088 PIPELINED

ARCHITECTURE INCREASES SYSTEM

PERFORMANCE

Figure

1-3

shows how programs are executed

over time in a standard microprocessor.

First, the microprocessor must fetch the

instruction to be performed, then it executes

the instruction. Only after the execution

is

complete

is

the CPU ready to fetch in the

next instruction, execute that instruction, etc.

as the program proceeds from beginning to

end.

The

CPU

hardware that executes instruc-

tions

must obviously wait until

the

instruction

is

fetched and decoded before

execution begins. Therefore, in standard

microprocessors, the execution hardware

(primarily the control circuitry and the

arithmetic and logic unit) spends a lot of time

waiting for instructions to be fetched. The

8088

eliminates this wasted time by dividing

the internal CPU into

two independent func-

tional units (Fig.

1-4).

EXECUTION

~STRUCTION

BUS

INTERFACE

UNIT PIPELINE

UNIT

V

SYS1EM

BUS

PIPELINED ARCHITECTURE DELIVERS HIGHER

PERFORMANCE

WITH REDUCED BUS

"DEAD

TIME"

Figure 1-4. Pipelined Internal Architecture

FETCH

EXECUTE

FETCH··

•

Figure 1-3. Program Execution

in

Standard Microprocessor

1-2