Section 16 Renesas Serial Peripheral Interface

R01UH0134EJ0400 Rev. 4.00 Page 839 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

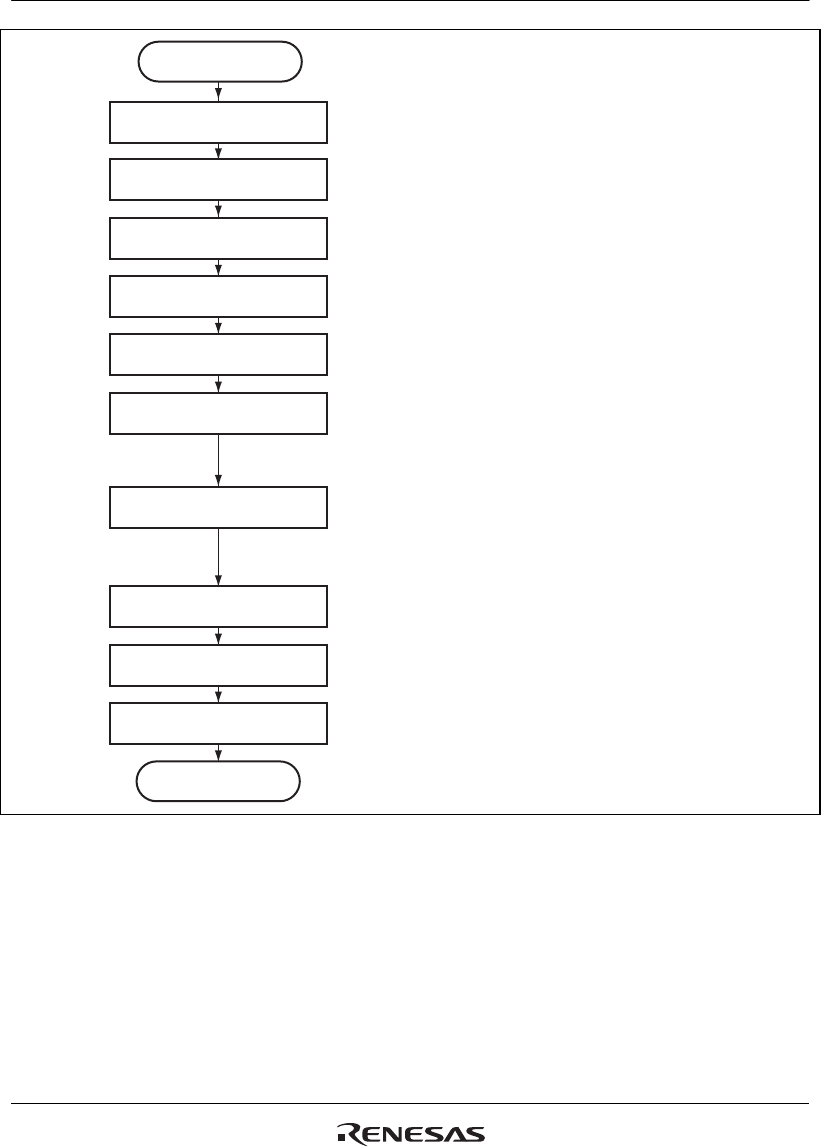

Set the pin control

register (SPPCR)

Set the bit rate

register (SPBR)

Set the data control

register (SPDCR)

Set the RSPCK delay

register (SPCKD)

Set the slave select negate

delay register (SSLND)

Set the next-access delay

register (SPND)

Set the command registers

0 to 3 (SPCMD0 to SPCMD3)

Set the control

register (SPCR)

Set the interrupt controller

Set the direct memory

access controller

Start of intialization in

master mode

• Sets MOSI signal value when transfer is in idle state.

• Sets SSL signal level.

• Sets RSPCK delay enable.

• Sets SSL negate delay enable.

• Sets next-access delay enable.

• Sets MSB or LSB first.

• Sets data length.

• Sets transfer bit rate.

• Sets clock phase.

• Sets clock polarity.

• Sets SSL negate delay value.

• Sets next-access delay value.

• Sets master mode.

• Sets interrupt mask.

(when using an interrupt)

(when using the direct memory

access controller)

• Sets transfer bit rate.

• Sets access width.

• Sets RSPCK delay value.

End of intialization in

master mode

Figure 16.17 Example of Initialization Flowchart in Master Mode